主要内容

自定义IP核心生成

生成一个HDL IP核心,包含HDL代码,用于在独立FPGA板上部署,Speedgoat板,Xilinx®Zynq.®-7000平台或英特尔®SOC设备

通过使用IP核心生成HDL Workflow Advisor中的工作流程,HDL Coder™可以生成IP核心,其中包含HDL源代码和用于将IP内核集成到EDK项目中的C头文件,然后编程目标硬件。

班级

话题

IP核心生成

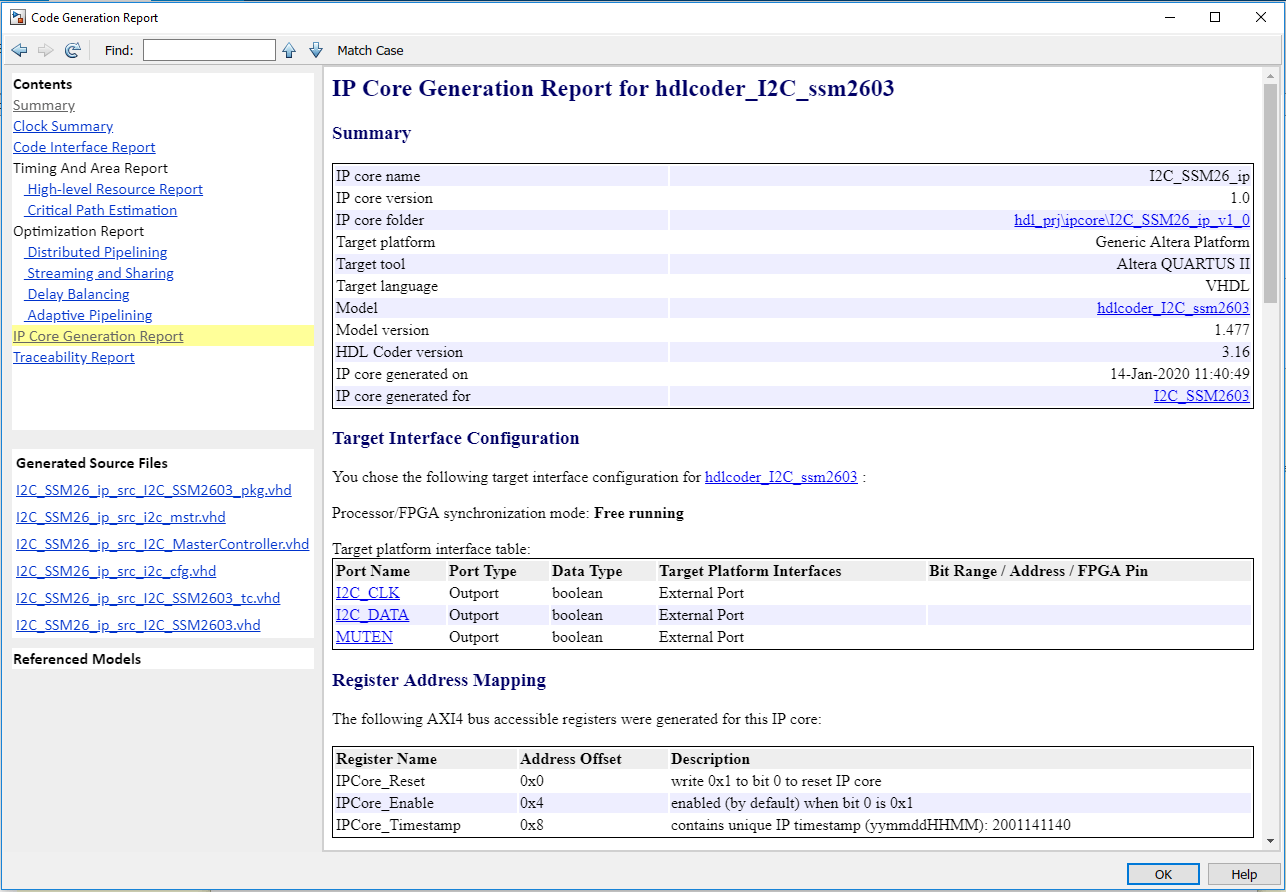

使用HDL Workflow Advisor,您可以从模型或算法生成自定义IP内核。

生成自定义IP核心时,默认情况下,您会生成HTML自定义IP核心报告。

了解使用具有IP核生成工作流的多个采样率的各种示例设计。

从Simulink模型生成独立的HDL IP内核万博1manbetx

当您打开HDL工作流程顾问并运行IP核心生成您的Simulink的工作流程万博1manbetx®模型,您可以指定通用Xilinx平台或通用Intel平台。

Matlab的董事会独立的IP核心生成®。

了解如何将DUT端口映射到多个AXI4流,AXI4流视频和AXI4主接口。

处理器同步和IP缓存

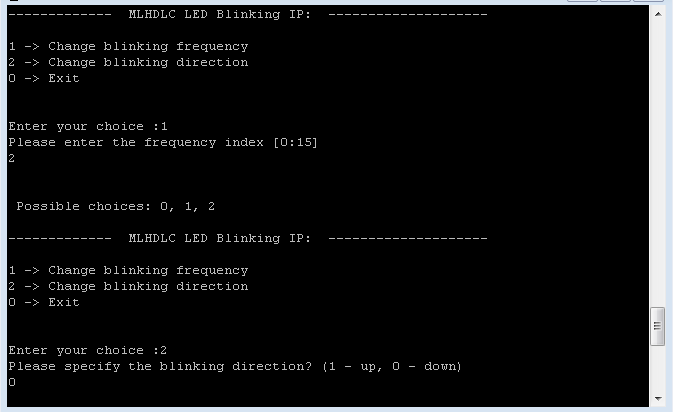

在HDL工作流程顾问中,您可以选择一个处理器/ FPGA同步模式对于您的处理器和FPGA时:以下同步模式可用:

了解HDL编码器如何自动插入逻辑以将全局复位信号同步到IP核心时钟域。

使用IP缓存来加速通过上下文的工作流程来加速参考设计合成时间。

故障排除

解决IP核心生成中的定时故障,Simulink实时FPGA I / O工作流程万博1manbetx

解决基于Vivado的电路板的IP核心生成工作流程的构建FPGA比特流步骤的时序故障或基于Vivado的板的Simulink实时FPGA I / O工作流程。万博1manbetx