生成FIFO接口DPI元器件为UART接收器

该示例示出了如何产生用于指与UART接收器。接口被写入MATLAB,并导出到HDL仿真被集成的FIFO缓冲器接口的SystemVerilog DPI组分完整的工作流程。还提供了UART接收器和试验台的SystemVerilog的文件。

为了说明的目的,本示例使用的Modelsim 10.3c在64位Windows 7然而,这种相同的方法可以很容易地复制的其他系统和模拟器。

要求和先决条件

s manbetx 845在这个例子中所需的产品:

MATLABCoder®

模拟器:导师Graphics®的ModelSim®/QuestaSim®或Cadence的精辟

一种支持的C编译器:微万博1manbetx软的Visual C ++或GNU GCC

背景

通用异步接收机和发射机(UART)是发送和通过串行线接收数据的电路。UART的,通常使用与RS-232标准和包含接收器和发射器。然而,在这个例子中仅一个接收器被使用。

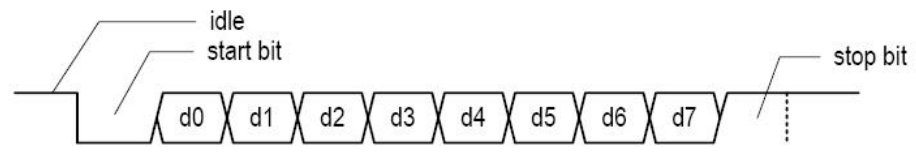

以“起始位”,这是0串行传输开始,后面跟数据位,和以“奇偶校验位”和一个单字节的“停止bit'.Transmission端是显示在如下图所示:

转印是异步的,这意味着没有时钟信息,所以接收器和发送器必须在什么波特率,停止位以及奇偶校验位被用于同意。在这个例子中一个字节将具有19200的波特率,则1个停止位和无奇偶校验位来传送。

过采样方案将被用来估计数据位的中间点的速度的16倍的波特率,如示于以下图中。

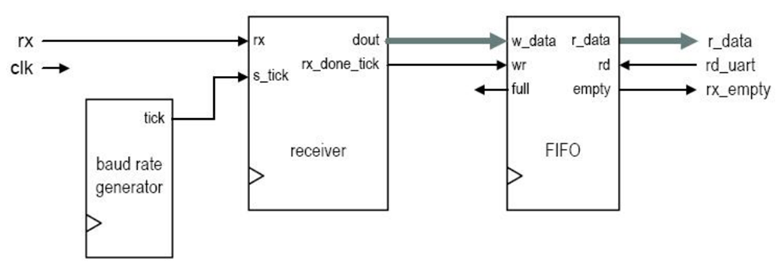

下面的示意图说明UART接收器的设计。

第一步:MATLAB设计

第一步是编写MATLAB代码,将满足您的要求设计,你应该尝试捕捉一个测试平台的要求。在这个例子中我们的设计由8个字的先入先出(FIFO)缓冲液中。

设计:FIFO_Buffer

试验台:FIFO_Buffer_tb

第2步:确保MATLAB测试平台捕获的要求

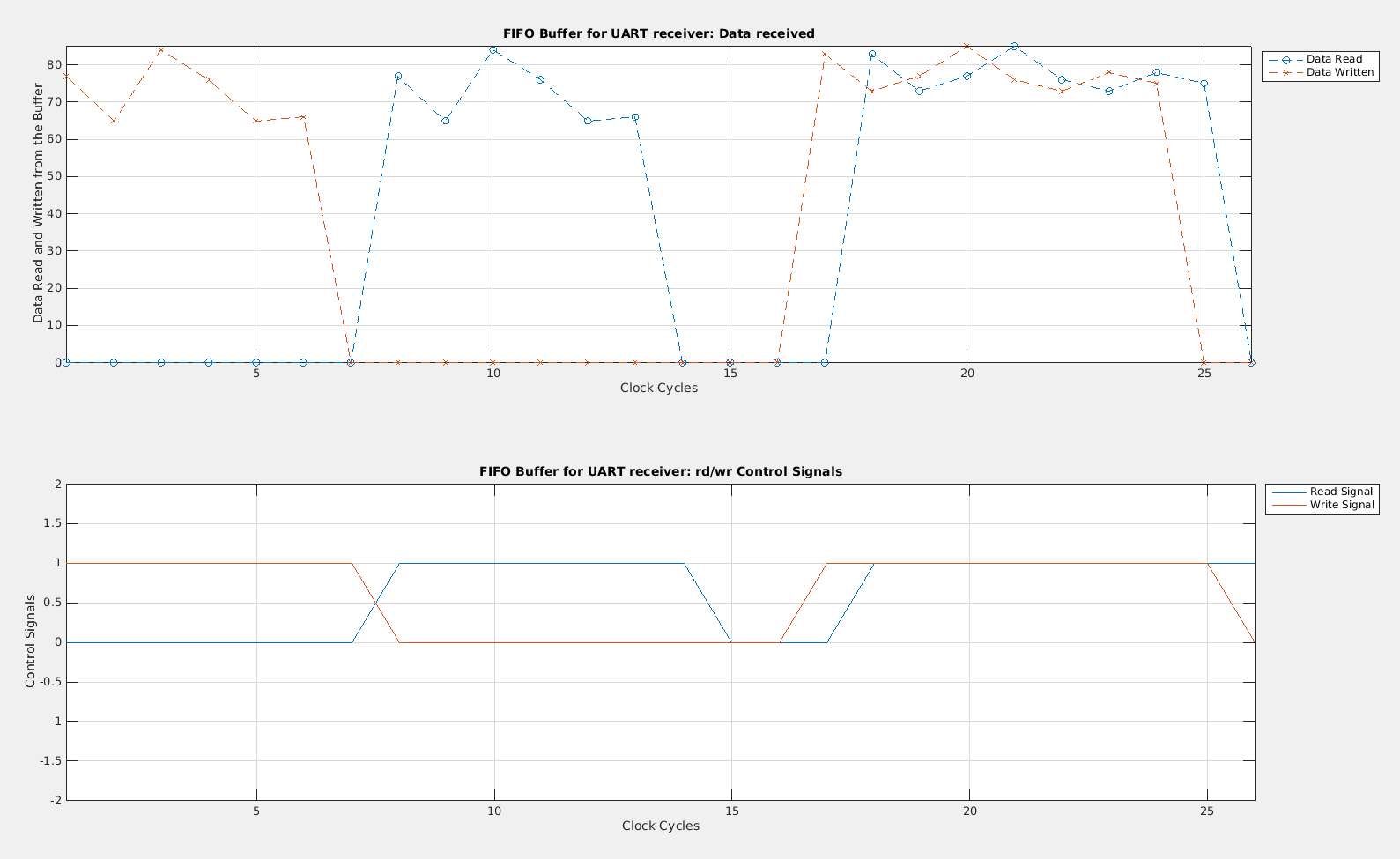

运行测试平台,以确保没有运行时错误,如下图所示,应绘制。

FIFO_Buffer_tb

注意,测试平台行使设计以下面的方式:*时钟周期<15:写6个字节(写入使能信号,读取信号被禁用),则读取6个字节(启用读取信号,写入信号禁用)。*时钟周期> 15:同时读写(例如:所写入的字节被读出在下一时钟周期)。

第3步:生成DPI组件并验证HDL模拟器行为

为了生成部件执行以下命令:

dpigen -testbench FIFO_Buffer_tb FIFO_Buffer -args {0,INT8(0),0}

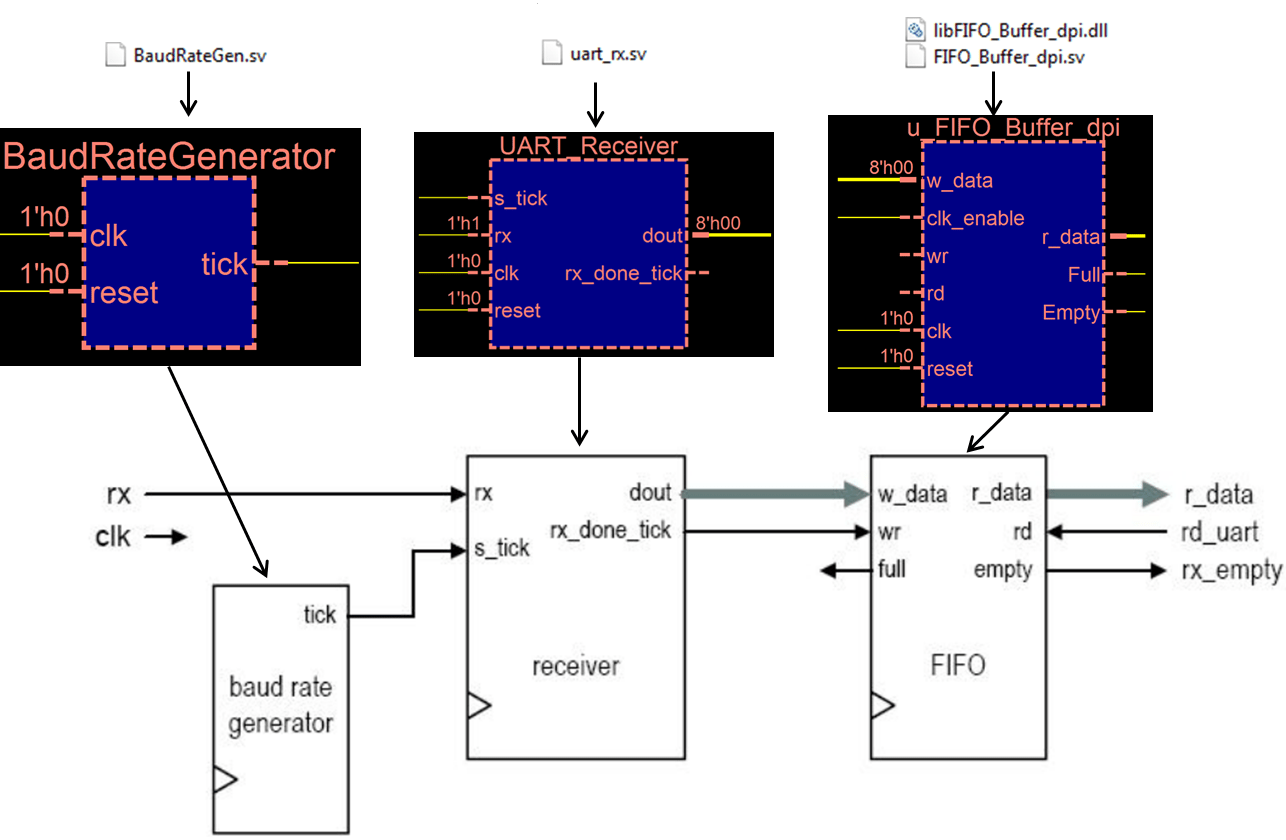

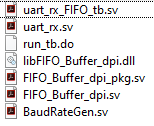

下图显示了在这个例子中的相关文件。

一旦DPIGEN产生DPI组件及其测试平台,您可以通过以下步骤,运行的SystemVerilog测试平台:

开始的ModelSim / QuestaSim在GUI模式。

更改你的HDL仿真器的代码生成目录下的当前目录切换到“dpi_tb”。

输入以下命令来启动你的模拟

做run_tb_mq.do

下面波形式将生成:

请注意,这是我们的测试平台MATLAB,我们写6个字节,然后读取它们,然后同时写入和读取8个字节匹配。

当模拟完成后,你应该看到在控制台打印以下文字:

**************测试已完成(通过)**************

步骤4:把生成的DPI组件到UART接收器设计

在DPI组件行为已经被验证之后,现在是时候将它集成到UART接收器。下图显示了所需的不同组件的文件。

将运动与集成的DPI组件的UART接收器,已经提供了一个名为“uart_rx_FIFO_tb.sv”的测试平台。为了整合所需要的组件的所有是实例在测试平台组件如下所示:

//实例DUT产生用MATLAB基于SystemVerilog的DPI FIFO_Buffer_dpi u_FIFO_Buffer_dpi(.clk(CLK),.clk_enable(clk_enable),.reset段(复位),.wr(rx_done_tick),.w_data(DOUT),.rd(RD)。空(空),.r_data(R_DATA)。全(全));

步骤5:模拟UART接收器

为了成功地进行设计仿真,请确保以下文件在同一文件夹:

类似于步骤3,开放的ModelSim和使用运行。做文件:

做run_tb.do

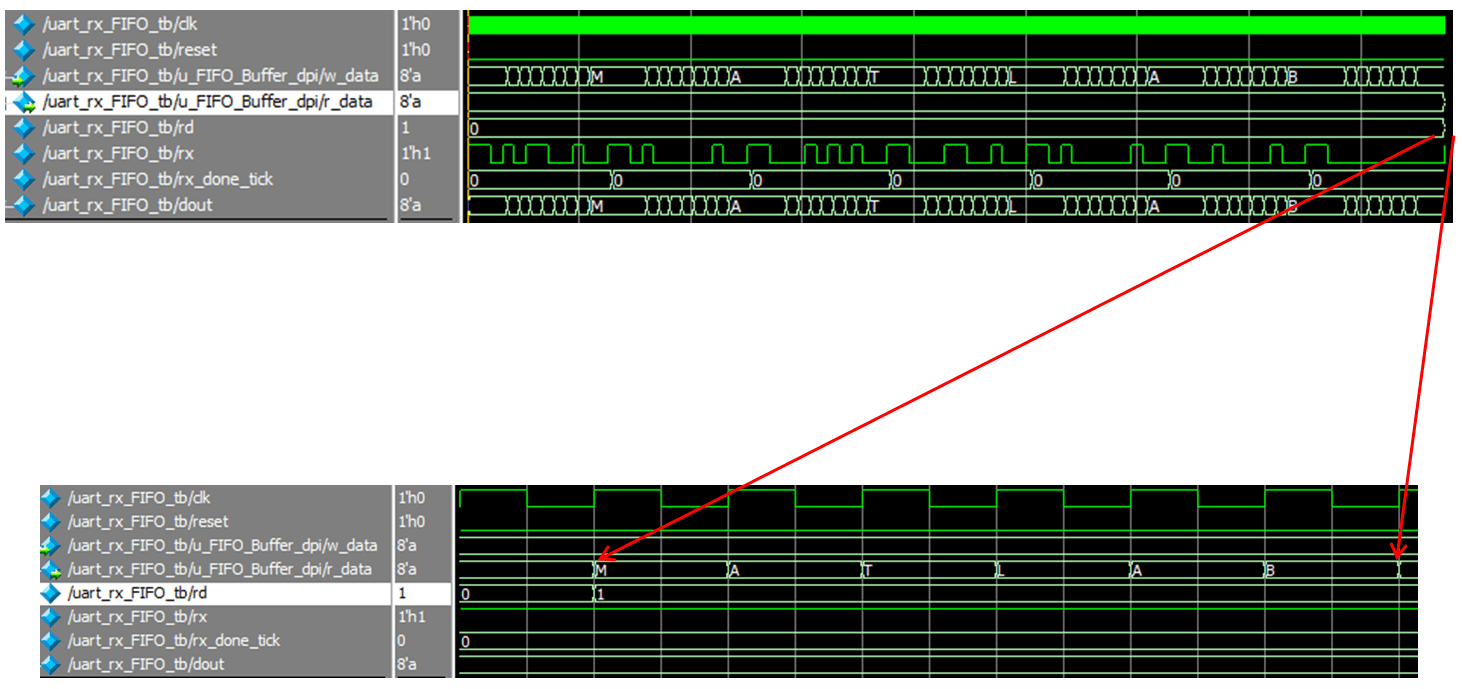

下面波形式产生:

在测试平台6 ASCII字母(“MATLAB”)经由串行“RX”信号传输,并写入到FIFO缓冲器。第六届信传输完成后,“RD”信号被肯定,得到的字母(“MATLAB”)早在“R_DATA”。

参考

傍P.储(2008),FPGA原型由Verilog实例。新泽西州霍博肯市:John Wiley和Sons,Inc.的