从Simulink生成参数化UVM测试台万博1manbetx

此示例演示如何在Simulink中开发设计和测试平台,并使用生成通用验证方法(UVM)环境的等效仿真万博1manbetxuvmbuild.相关示例展示了如何扩展此测试台,以使用特定于协议的驱动程序、受约束的随机序列和参数化记分牌来改进验证。

介绍

这个示例将带领您完成一个自顶向下的HDL实现设计开发过程。在这样的工作流中,您可以在Simulink中设计一个行为算法,并使用周围的块对其进行测试,以生成刺激和检查结果。万博1manbetx一旦模拟确认设计满足其需求,您就可以向下游HDL实现团队交付任何所需的附属品。您需要重新验证HDL实现是否满足在Simulink中模拟的需求,以及设计的任何其他独特方面,如未在Simulink中建模的协议接口。万博1manbetx

通常,传递过程是乏味的,并且是许多错误的来源。HDL实现和HDL设计验证(DV)工程师必须:

将书面规范翻译为HDL和测试环境。

了解Simulink仿真环境的运行时行为,例如如何创建、处理和检查刺激。万博1manbetx

将运行时行为转换为SystemVerilog实现。

将刺激、设计和响应检查集成到一个可运行的SystemVerilog中,以确认转换后的行为与原始Simulink模拟的行为相同。万博1manbetx

将这些主要SystemVerilog组件集成到UVM上下文中,以允许使用DV编写的验证扩展Simulink测试。此扩展测试可能包括随机测试、SystemVerilog断言、功能覆盖率和代码覆盖率万博1manbetx。

使用HDL Verifier UVM生成功能,此切换过程是自动化的。DV工程师获得一个经过验证的UVM测试环境,该环境与Simulink中执行的测试相匹配,并且可以轻松地更新该环境以满足其下游验证需求。万博1manbetx

在Simulink中进行设计和测试万博1manbetx

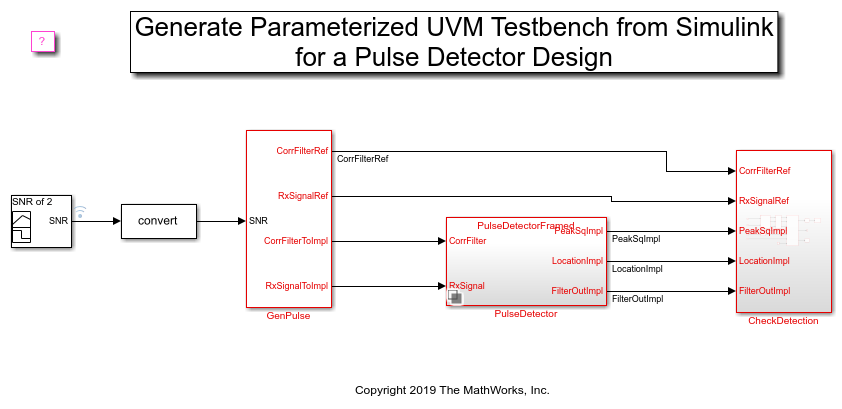

编写您的算法并向其添加测试台。该模型由试验台的典型子系统组成,如刺激生成、被测设计(DUT)和响应检查。

在本设计中,源子系统在5000个样本帧的随机位置创建一个64个样本信息的随机脉冲。它还产生一组64个最优匹配滤波器系数检测脉冲。输入数据同时提供给设计和响应检查器。响应检查器验证脉冲在噪声波形中的正确位置被检测到。通过控制台输出确认正确操作。如果检测到的信号的预期功率不在一定的范围内,就会触发断言。

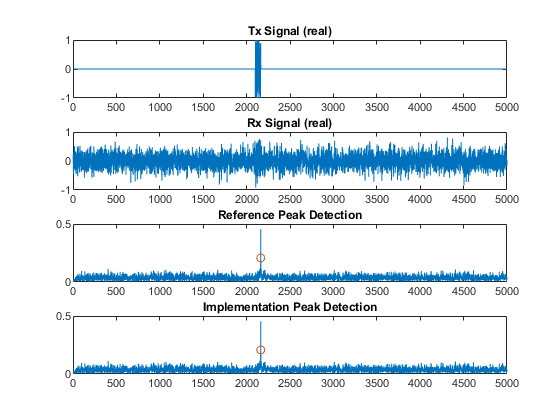

模拟该模型可以证实在五个产生的脉冲中,有五个被探测到。一个三面板图显示了一个Tx信号(原始脉冲),一个Rx信号(嵌入在噪声中的脉冲),以及一个参考实现的滤波输出,该参考实现显示了检测到峰值的位置。输出信号被延迟一帧。

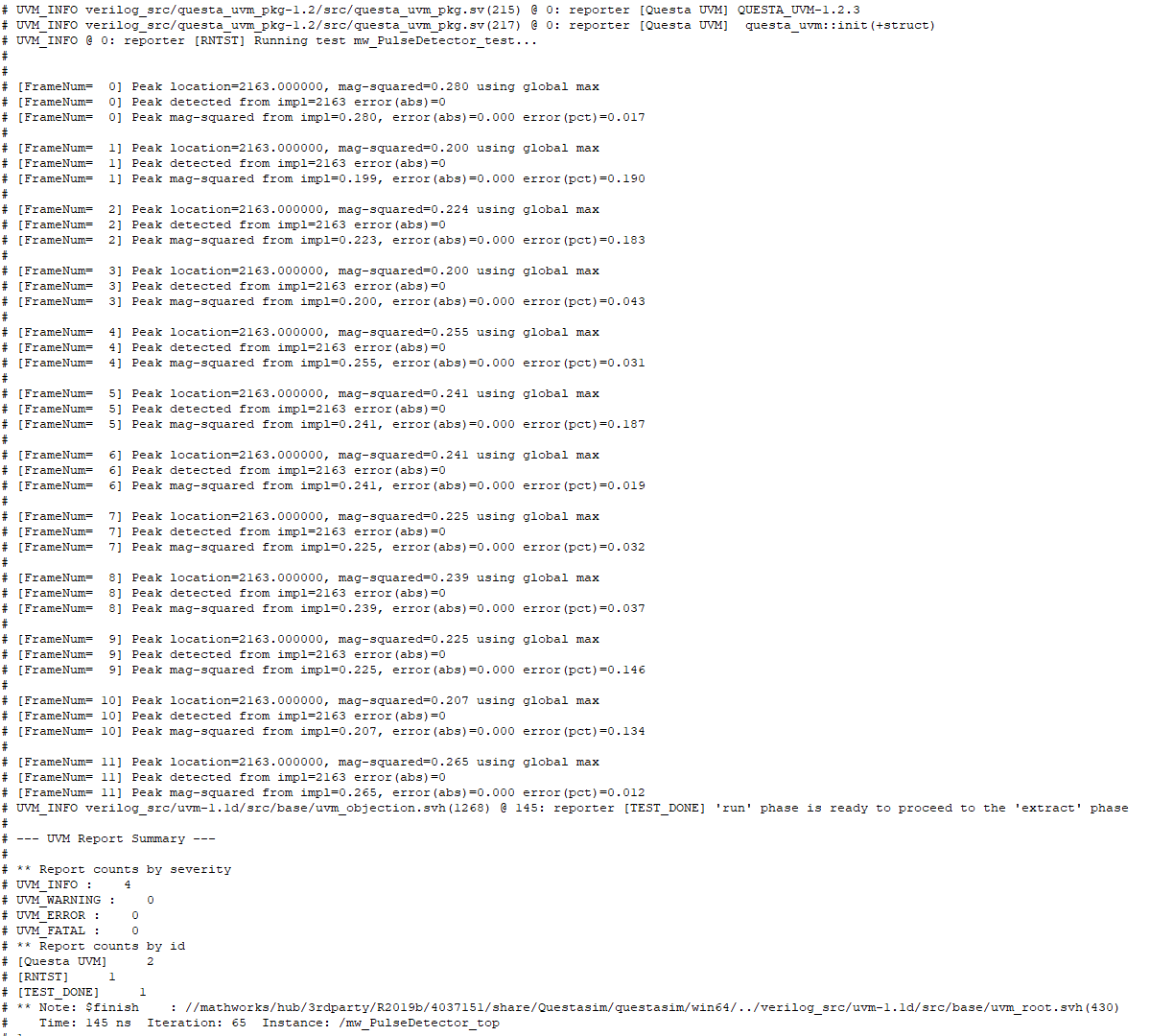

[FrameNum=0]峰值位置=2163.000000,使用从IMP检测到的全局最大值[FrameNum=0]峰值时的mag平方=0.280,从IMP检测到的误差(abs)=0[FrameNum=0]峰值mag平方=0.280,从IMP检测到的误差(abs)=0.017[FrameNum=1]峰值位置=2163.000000,使用从IMP检测到的全局最大值[FrameNum=1]峰值时的mag平方=0.200,从IMP=2163误差(abs)=0[FrameNum=1]峰值mag从IML=0.199的平方,误差(abs)=0.000误差(pct)=0.190[FrameNum=2]峰值位置=2163.000000,mag平方=0.224使用全局最大值[FrameNum=2]从IML检测到的峰值mag=2163误差(abs)=0[FrameNum=2]峰值mag从IMP的平方=0.223,误差(abs)=0.000误差(pct)=0.183峰值位置=2163.000000,mag平方=0.200,使用从IML检测到的全局最大[FrameNum=3]峰值误差(abs)=0[FrameNum=3]峰值mag平方从IML=0.200,误差(abs)=0.000误差(pct)=0.043[FrameNum=4]峰值位置=2163.000000,mag平方=0.255,使用从IML检测到的全局最大[FrameNum=4]峰值误差(abs)=0[FrameNum=4]使用全局最大值[FrameNum=5]从IMP检测到的峰值[FrameNum=5]从IML=2163错误(abs)=0[FrameNum=5]从IMP检测到的峰值mag平方=0.255,误差(abs)=0.000误差(pct)=0.241,误差(abs)=0.000误差(pct)=0.187[FrameNum=6]峰值位置=2163.000000,mag平方=0.241使用全局最大[FrameNum=6]从IMP检测到的峰值=2163错误(abs)=0[FrameNum=6]从IMP检测到的峰值mag平方=0.241,错误(abs)=0.000错误(pct)=0.019[FrameNum=7]峰值位置=2163.000000,mag平方=0.225使用全局最大[FrameNum=7]从IMP检测到的峰值=2163错误(abs)=0[FrameNum=7]使用全局最大值[FrameNum=8]从IMP检测到的峰值[FrameNum=8]从IMP=2163错误(abs)=0[FrameNum=8]从IMP检测到的峰值,误差(abs)=0.000误差(pct)=0.032[FrameNum=8]峰值位置=2163.000000,mag平方=0.239,误差(abs)=0.000误差(pct)=0.037[FrameNum=9]峰值位置=2163.000000,mag平方=0.225,使用从IMP检测到的全局最大[FrameNum=9]峰值=2163错误(abs)=0[FrameNum=9]峰值mag平方从IMP=0.225,错误(abs)=0.000错误(pct)=0.146[FrameNum=10]峰值位置=2163.000000,使用从IMP检测到的全局最大[FrameNum=10]峰值=0.207错误(abs)=0[FrameNum=10]峰值mag与impl的平方=0.207,误差(abs)=0.000误差(pct)=0.134

生成可执行的UVM测试台

使用uvmbuild函数将您的设计导出到UVM环境。UVM测试台为HDL验证过程提供了结构,并允许实现验证团队重用所有的Simulink测试台组件和测试用例。万博1manbetx标准组件定义根据环境的各个部分在模拟中的角色将它们分开。对于这个示例:

PulseDetector映射到DUT SystemVerilog模块GenPulse子系统被映射到sequence_item为Sequencer UVM组件创建CheckDetection子系统映射到记分板UVM组件。

生成的UVM测试台如下所示:

%生成UVM测试台设计=“prm_uvmtb / PulseDetector”序列=“prm_uvmtb/GenPulse”记分板=“prm_uvmtb / CheckDetection”uvmbuild(设计、顺序、记分板)

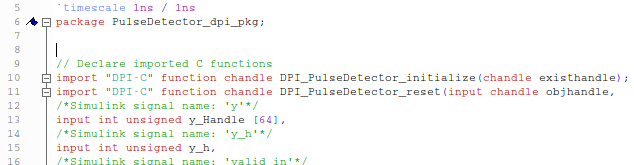

UVM测试台的每个突出显示部分都是通过包装Simulink子系统生成的C代码并使用DPI调用其入口点来实现的。下图显示了PulseDetector子系统的两个函数声明。万博1manbetx

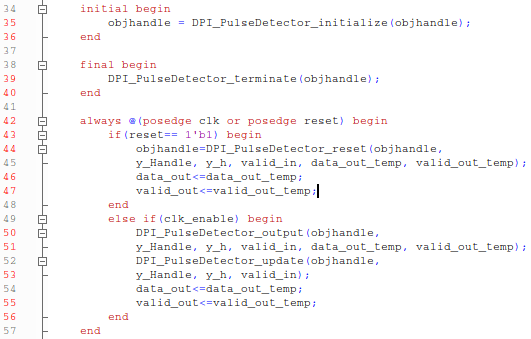

SystemVerilog/UVM代码确定DPI调用的计时。例如,在PulseDetector SystemVerilog模块中:

“initialize”DPI调用是由“initial”代码块触发的。

"terminate" DPI调用由"final"代码块触发。

“reset”DPI调用由主动复位信号触发。

“输出”和“更新”DPI调用是由一个上升的时钟边缘触发的,其中复位不活跃,时钟使能是活跃的。

运行UVM测试台

的uvmbuild该过程还生成一个脚本来运行UVM测试的模拟。为以下模拟器生成脚本:

Mentor Graphics®Modelsim®和Questa®:run_tb_mq.do

节奏®门齿™:run_tb_incisive.sh

节奏®Xcelium™:run_tb_xcelium.sh

Synopsys对此®VCS®:run_tb_vcs.sh

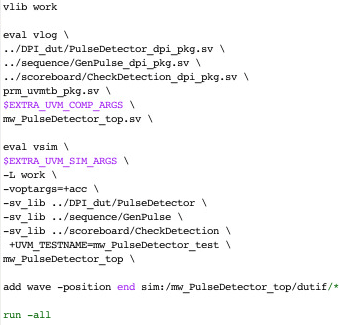

显示为ModelSim生成的脚本。

执行生成的脚本以验证UVM执行与Simulink执行的匹配。万博1manbetx因为序列是用信噪比输入端口参数化的,在UVM中它的默认值将是0.0。为了正确地比较模拟运行,我们需要将其默认值更改为2.0(它有一个位值0b10_000000),以匹配Simulink;万博1manbetx这可以通过一个plusarg来完成,我们通过一个环境变量传递给脚本。

%清除影响UVM模拟的环境变量'环境变量EXTRA_UVM_SIM_ARGS环境变量EXTRA_UVM_COMP_ARGS环境变量UVM_TOP_MODULE

%使用2.0的信噪比模拟UVM测试台cdprm_uvmtb_uvmbuild uvm_testbench /环境变量EXTRA_UVM_SIM_ARGS+ SNR_default_inp_val = 10000000!vsim - run_tb_mq。do % ModelSim/QuestaSim (gui)!Vsim -c -do run_tb_mq。做% ModelSim/QuestaSim(控制台)! ./运行_tb_incisive.sh%incisive(控制台)!./run_tb_xcelium.sh%xcelium(控制台)!./run_tb_vcs.sh % VCS (console)cd. . / . . / . .

模拟日志显示相同的诊断消息:

波形显示了DUT接口信号的时序。光标被放置在帧边界,并显示匹配滤波器系数的瞬时更新。