使用联合模拟比较HDL和Simuli万博1manbetxnk代码覆盖率

此示例显示如何使用Simulink®和HDL模拟器实现HDL巡航控制器设计的完整代码覆盖。万博1manbetx

介绍

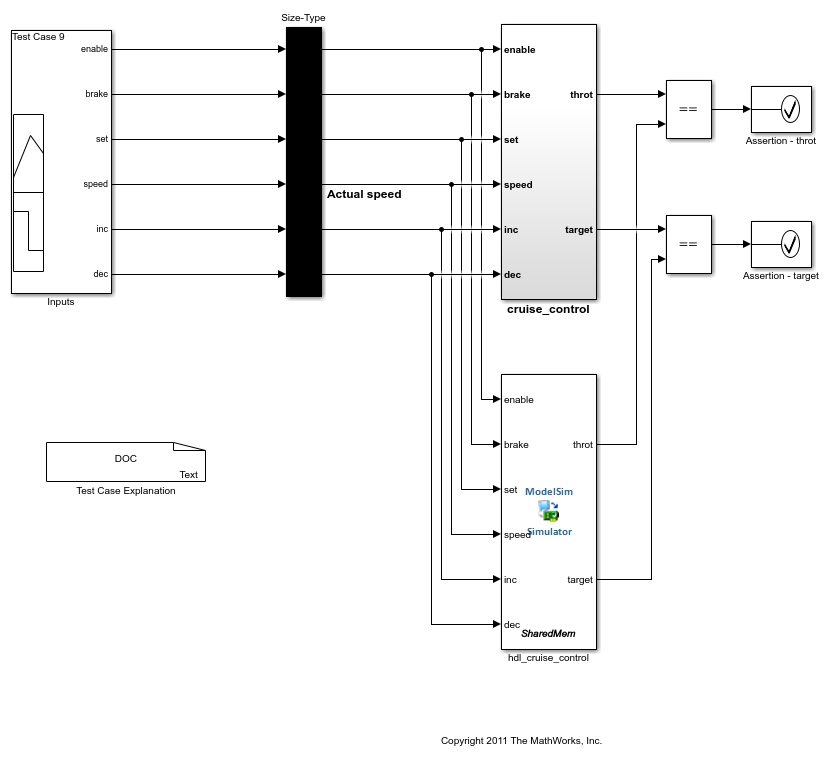

与此模型关联的HDL代码通过HDL编码器生成™ 来自巡航控制器的Simulink行为模型。提供了一个测试台模型,通过比较HDL协同模拟块的输出与原始行万博1manbetx为块的输出来验证HDL代码的正确性。测试台模型中的测试用例通过Simulink Design Verifier生成™ 从原始行为模型获得完整的模型覆盖率。此示例显示自动生成的测试用例也实现了完整的HDL代码覆盖率。运行此示例不需要安装Simulink Design Verifier。

打开Simulin万博1manbetxk模型

如果您正在使用ModelSim或QuestaSim,则模型巡航控制模块SIM.slx应该是打开的。如果您使用的是Incisive或Xcelium,请关闭ModelSim模型并打开模型巡航控制切迹.slx.

请注意,代码覆盖功能是ModelSim PE中的可选功能。确保您的ModelSim版本具有运行此示例的正确代码覆盖率许可证。

ModelSim %:modelName =“巡航控制系统模型SIM”;open_system (modelName);

%对于尖锐的:modelName =“cruise_control_incisive”;open_system (modelName);

在HDL模拟中设置时钟、重置和时钟启用

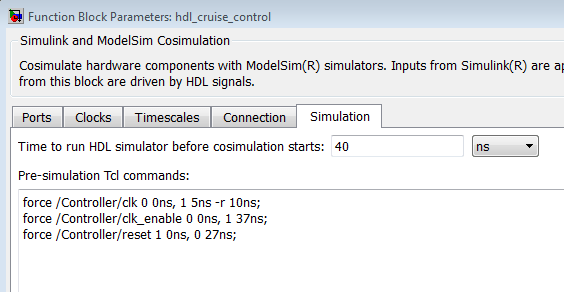

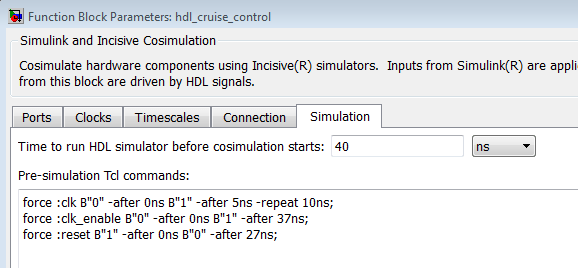

时钟、复位和时钟启用信号不属于Simulink模拟的一部分。我们使用联合模拟块掩码“模拟”选项卡中的“预模拟Tcl命令”为它们万博1manbetx定义驱动程序。我们还设置了“联合模拟开始前运行HDL模拟器的时间”这样,在交换任何输入和输出数据值之前,HDL已成功脱离复位。

对于ModelSim:

对于尖锐的:

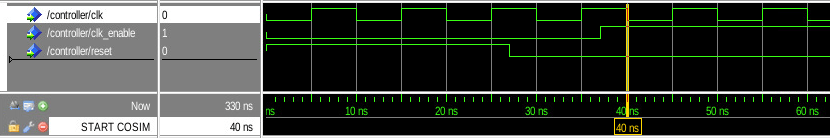

以HDL表示的结果波形:

Tcl force命令用于生成控制信号的波形:

时钟周期为10纳秒

时钟使能信号在37纳秒时是有效的。

复位信号在0到27纳秒之间断言。

联合模拟的开始时间应该与HDL时钟的下降沿对齐,以避免竞争条件,因为HDL信号在HDL时钟的上升沿改变它们的值。因此,该参数取值为10ns时钟周期的整数倍。

我们还希望在重置之后运行HDL设计,但在clk_enable启用的第一个活动时钟边缘之前停止。这是为了匹配行为块,它会在模拟开始后立即更新其内部状态。

基于上述考虑,选项“联合模拟开始前运行HDL模拟器的时间”设置为40 ns。运行每个测试用例时,“预模拟Tcl命令”首先在HDL模拟器中应用。然后,HDL模拟器将其时间提前40 ns,以便在协同模拟开始之前应用重置、时钟和clk_启用信号。

启动HDL模拟器进行联合仿真

对于Modelsim:

%在启用代码覆盖率的情况下编译和调用Modelsim的命令。tclCmds = {“vlib工作”,...%创建ModelSim库“vcom+覆盖巡航\u hdlsrc/PI\u控制器。vhd”,...%编译启用代码覆盖的VHDL代码“vcom+覆盖巡航_hdlsrc/Controller.vhd”,...%编译启用代码覆盖的VHDL代码“v万博1manbetxsimulink报道工作。控制器的,...%负荷模拟'将“准备好进行联合模拟…”,...};%现在我们启动HDL模拟器,等待它准备就绪。vsim(“tclstart”, tclCmds);disp (“等待HDL模拟器启动……”);processid=pingHdlSim(240);disp(“HDL模拟器已经准备好进行共同模拟了。”);

对于尖锐的:

%在启用代码覆盖率的情况下编译和调用Incisive的命令。tclCmds = {'exec ncvhdl-64位-v93巡航控制器hdlsrc/PI控制器.vhd',...%编译VHDL代码'exec ncvhdl-64位-v93巡航_hdlsrc/Controller.vhd',...%编译VHDL代码“exec ncelab-64位-全覆盖-vhdl\u时间\u精度1ns-访问+wc控制器”,...%精心设计并启用覆盖“hdl万博1manbetxsimulink -covoverwrite控制器”,...%负荷模拟'将“准备好进行联合模拟…”,...};%现在我们启动HDL模拟器,等待它准备就绪。nclaunch (“tclstart”,tclCmds,“runmode”,“CLI”,“libfile”,“liblfihdls_gcc44.so”); disp(“等待HDL模拟器启动……”);processid=pingHdlSim(240);disp(“HDL模拟器已经准备好进行共同模拟了。”);

运行仿真

在测试台模型中有9个测试用例。此示例使用所有测试用例运行此模型,以生成代码覆盖率结果。在完成每个协同仿真会话后,不需要重新启动HDL模拟器,因为在每次仿真开始时HDL信号会被正确地重置。每次模拟之后,都会添加一个短暂的暂停,以确保HDL模拟器有时间在下一次迭代之前更新覆盖结果。

%运行协同模拟对于k=1:9信号生成器([modelName' /输入'],“activegroup”,k);选择一个测试用例sim(型号名称);%运行模拟暂停(5);将覆盖率写入数据库时暂停终止

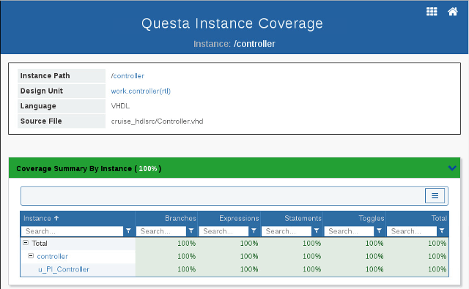

观察代码覆盖率结果

当我们迭代所有测试用例时,HDL模拟器会累积覆盖率。当模拟完成时,代码覆盖率达到100%。

对于ModelSim:您可以在UI的“coverage”选项卡中检查覆盖率结果。

对于尖锐的:我们转储覆盖结果,并使用“imc”工具来可视化结果。

%转储并可视化覆盖率结果TCLHDLISM(覆盖您测试的);系统('imc -gui -负载测试&');