入门自定义生成的SystemVerilog代码

此示例显示了如何在SystemVerilog DPI组件生成过程中自定义生成的SystemVerILog代码。

要求和先决条件

s manbetx 845此示例所需的产品:

MATLAB®.

万博1manbetxSimulink®.

万博1manbetx仿真软件编码器™

MentorGraphics®SexchingIm®/Questasim®

支持的C编译器之一:M万博1manbetxicrosoft®VisualC++或GNU GCC

背景

如果默认生成的SystemVerilog代码不符合您的要求,则可以选择自定义生成的代码。此示例显示如何自定义生成的代码。

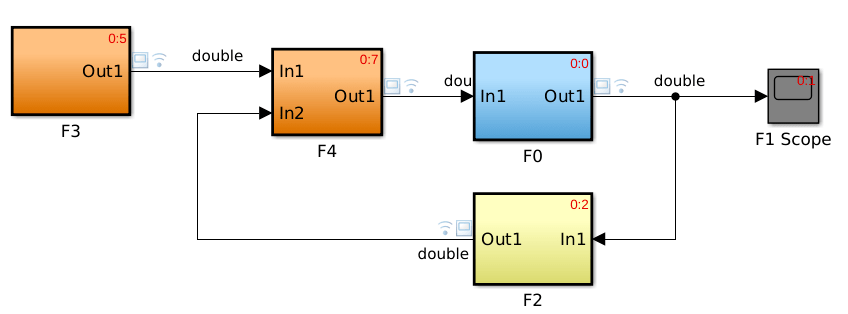

在以下Simulink模型中,与子万博1manbetx系统,F0,F2,F3和F4相对应的生成的代码将单独导出为SystemVerilog模块。默认情况下,每个模块包含三个控制信号:时钟,时钟启用和重置。在HDL仿真中,将在时钟信号的上升沿调用子系统更新和输出功能。事件调度程序将以与Simulink模型中的相同序列触发HDL模拟器中的那些更新和输出功能。万博1manbetx

开放的例子

运行以下代码以打开设计

Open_System('svdpi_simplefeedback');

为代码生成设置模型

从SVPID_SI万博1manbetxMPLEFEDBACK模型打开Simulink Model配置参数面板。设置以下参数:

选择代码生成 - >系统目标文件。单击“浏览”按钮,然后选择“systemverilog_dpi_grt.tlc”。

在Toolchain设置中,如果您使用的是Windows,或者使用Linux,请选择一个Visual Studio版本。确保未选中“仅生成代码”选项。

选择代码生成 - > SystemVerilog DPI,并检查“自定义生成的SystemVerilog代码”选项。确保将“源文件模板”设置为默认模板“svdpi_event.vgt”。

您还可以单击“编辑”按钮以查看默认SystemVerilog模板。

现在我们已经完成了配置参数面板。点击“确定”按钮关闭它。

生成SystemVerilog DPI组件

在“svdpi_SimpleFeedBack”模型中,为子系统F0、F2、F3和F4生成C代码。你可以通过在MATLAB中运行以下命令从命令行生成C代码:

SLBUILD('svdpi_simplefeedback / f0')SLBUILD('svdpi_simplefeedback / f2')SLBUILD('svdpi_simplefeedback / f3')SLBUILD('svdpi_simplefeedback / f4')

现在,这些子系统的C代码分别在子目录“f0_build”,“f2_build”,“f3_build”和“f4_build”中生成。

试验台的文件

在TestBench“SimpleFeedback_TB.SV”中,控制信号连接,使其从具有较高执行顺序的模块流到模拟到模拟在Simulink中执行顺序的模块。万博1manbetx

运行生成的测试工作台

以GUI模式启动ModelSIM / Questasim并将目录更改为MATLAB中的当前目录。在Modelsim / Questasim中,输入以下命令以编译您的设计

做build.do.

在ModelSim/QuestaSim中,输入以下命令来模拟您的设计

做sim.do.

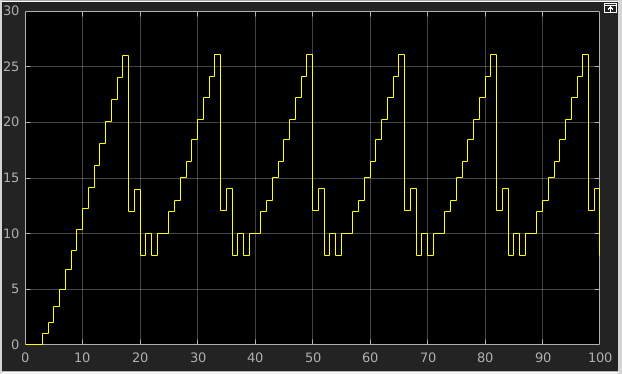

仿真完成后,您可以考生每个子系统的输出和ImpentiM的波形窗口中捕获信号之间的差异。