Sobel边缘检测算法与计算机视觉工具箱

这个例子展示和解释“自上而下”设计出适用于Sobel边缘检测算法的方法。索贝尔边缘检测算法是一种流行的且简单的边缘检测算法,是本实施例的重点。有了这个例子中,你将了解到:

如何Si万博1manbetxmulink®允许您设计一个系统级的数字信号处理(DSP)算法。

如何详细阐述设计,使其在硬件上可实现。

如何在Simulink环境中与ModelSim®或Cadence®Incisive®协同模拟手写的HDL代码(对应于您的Simu万博1manbetxlink模型)。

该方法是。的一个例子基于模型的设计。要了解更多关于基于模型的设计参考//www.tianjin-qmedu.com/model-based-design

您需要以下产品来运行示例中的所有模型:s manbetx 845

MATLAB®

万博1manbetx

定点设计™

HDL验证™

计算机视觉工具箱™

DSP系统工具箱™

的ModelSim SE或PE。Cadence公司或精辟

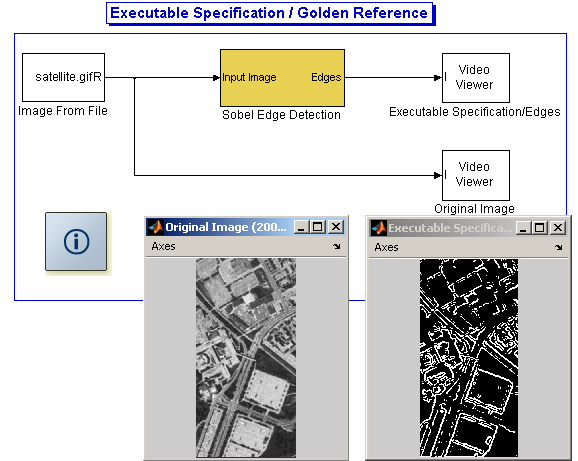

Sobel边缘检测算法的可执行规范

随着设计变得越来越大、越来越复杂,有必要在高层次上描述设计。这种高水平的描述不仅使设计师模拟运行得更快,也可以在整个开发过程用于验证。这个结果的过程允许开发者在早期识别错误,避免昂贵的错误发现末期开发。这种高层次的设计通常由系统工程师来完成。

为了实现在硬件,如ASIC或FPGA应用DSP算法,系统级工程师首先设计了算法和验证,该算法满足项目需求。这种设计后来成为负责采取算法,硬件工程师的黄金参考。

在这个例子中,Sobel边缘检测算法已经在Simulink中实现。万博1manbetx打开可执行模型和“Sobel边缘检测”块上双击学习算法是如何在Simulink实现。万博1manbetx当将Sobel边缘检测块上双击,可以看到,该算法由两个二维过滤器,一个计算在列方向上的梯度(顶过滤器),一个用于计算在所述行方向上的梯度(下过滤)。这两个过滤器使用一个3x3内核。

这Simu万博1manbetxlink模型作为规范发展路径的其余部分。它是一个可执行的规范,这意味着您可以很容易地在Simulink环境中执行此模型。万博1manbetx

本例使用卫星图像作为边缘检测算法的输入。此图像用作输入测试向量,并在整个示例中使用。如果负责算法硬件实现的工程师也在Simulink环境中工作,那么在将测试向量移植到不同的应用程序或创建容易出现人为错误的测试用例时,就不需要额外的开销。万博1manbetx可执行规范中使用的测试工具在整个示例中使用。

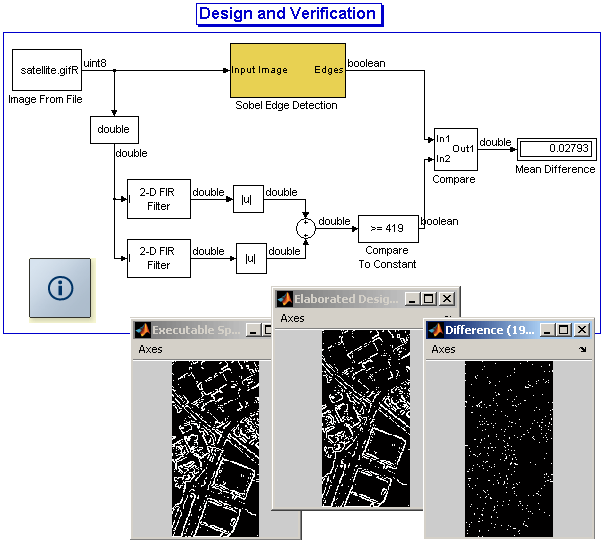

设计并验证了算法的实现

在设计可执行模型,系统工程师一般不会记住的实现细节,而是实现的算法匹配的行为要求。一旦系统工程师提交可执行规范给开发团队,开发团队可能需要进行修改,可执行的规范,以适应设计成一个实时系统可能已经有限的资源,如内存和处理能力。

在本例中,开发人员可能决定消除方形操作,用绝对值操作代替它们,以提高硬件实现的效率。这将导致协同模拟结果和黄金参考之间的差异,但为了本例,我们假设差异是可以接受的。打开边缘检测设计模型。你可以看到相同的测试向量作为仍在使用以前的模式。其结果可能对黄金参考很容易地验证。数值显示器显示金色的参考和新设计之间的平均差。

定点设计

由于我们的最终目标是在FPGA或ASIC中实现算法,我们必须将双精度设计转换为定点设计。这可以通过使用Simulink很容易地完成。万博1manbetx我们使用上一节中开发的双精度模型直接开发不引入任何新块的定点模型。万博1manbetxSimulink允许我们确定数据和数学操作的比特数和伸缩,并为分析系统的定点操作提供了良好的环境。

在该固定点设计中,输入到滤波器是一个带符号的9位整数,并将滤波器的输出是有符号的11位整数。如果每个计算块上双击,如过滤器或总和块,可以看到的是,显影剂可以很容易地调的比特宽度和缩放有关该块的内部计算。这给了巨大的杠杆作用,以设计师的黄金参考的输出匹配之间的妥协,而使用必需的比特数最少保存在设备上的区域。

打开定点模型并通过双击计算块(例如2D过滤器或加法块)并查看相应的定点面板来检查定点是如何实现的。

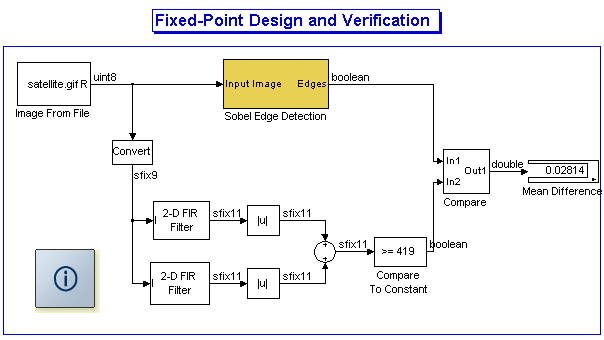

设计的精

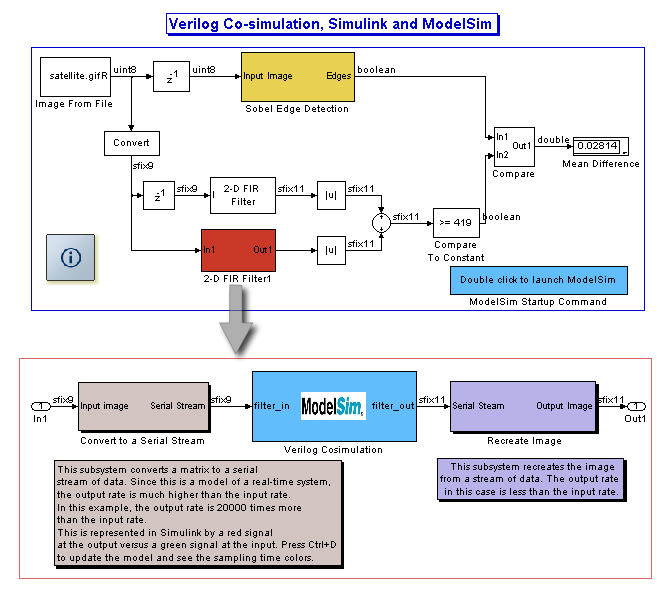

在我们的例子中,边缘检测算法的输入是一个大小为200x100的二维图像。在实时系统中,输入很可能不是一个矩阵,而是一个连续的数据流;例如,这种串行数据流可以由电荷耦合器件(CCD)产生。因此,我们需要修改设计结构,使边缘检测算法接受并对串行数据流进行二维滤波。

在这种情况下,我们首先序列化输入图像。然后我们对这些串行数据进行2D过滤。稍后我们将对数据流进行反序列化,以便能够将输出与黄金引用进行比较。要了解这是如何做到的,请参阅边缘检测细化模型。

此操作仅对底部过滤器执行。正如预期的那样,新的设计仍然产生和以前完全一样的结果。添加了两个延迟元素以补偿序列化器块中的抛光。本设计还展示了Simulink的多速率性能。万博1manbetx序列化块的输出采样率比输入块的采样率高20000倍。

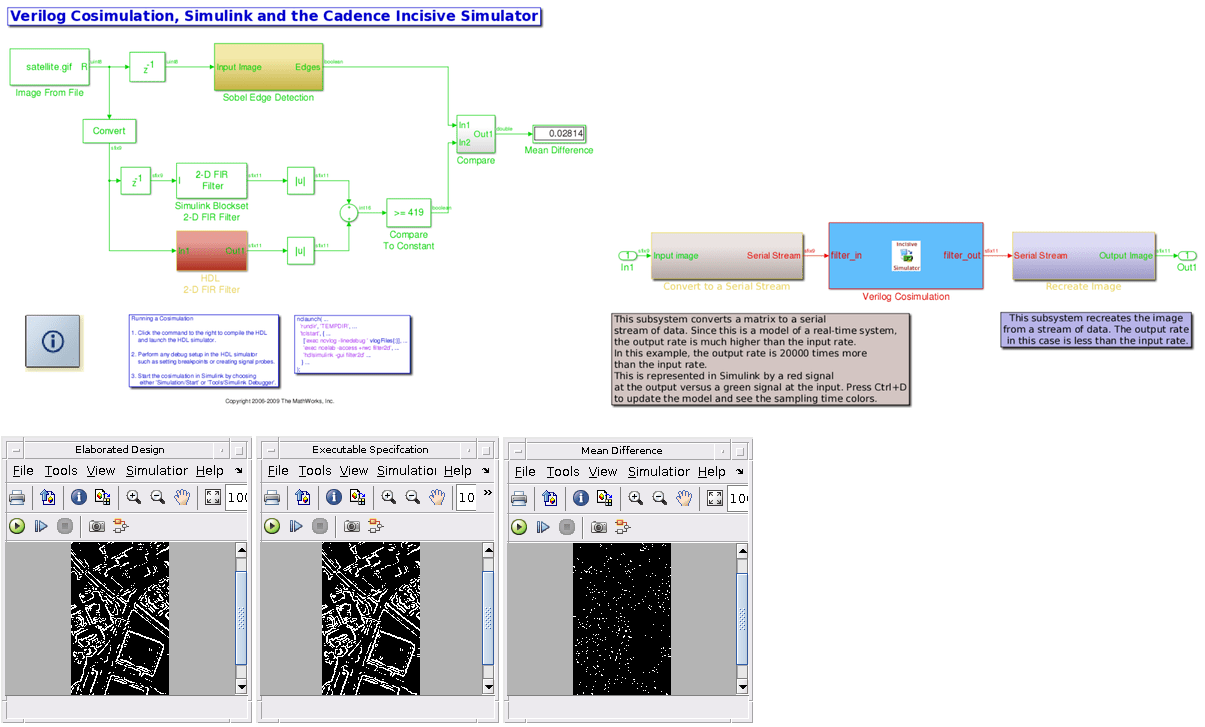

万博1manbetx仿真软件®Cosimulation

上一节的模型可以传递给HDL设计人员,使用上一节设计的2D过滤器编写相应的VHDL或Verilog代码。代码编写完成后,HDL设计人员可以使用HDL Verifier™在Simulink环境中使用ModelSim或Incisive模拟HDL设计,并将HDL设计的输出与可执行规范的输出进行比较。万博1manbetx注意,在这个过程中,没有必要生成一个HDL测试工作台。Simu万博1manbetxlink模型通过HDL验证器将输入的测试向量输入给ModelSim或Incisive,并从ModelSim或Incisive中提取数据返回到Simulink环境中。HDL设计器可以很容易地验证HDL代码是否按照规范运行。

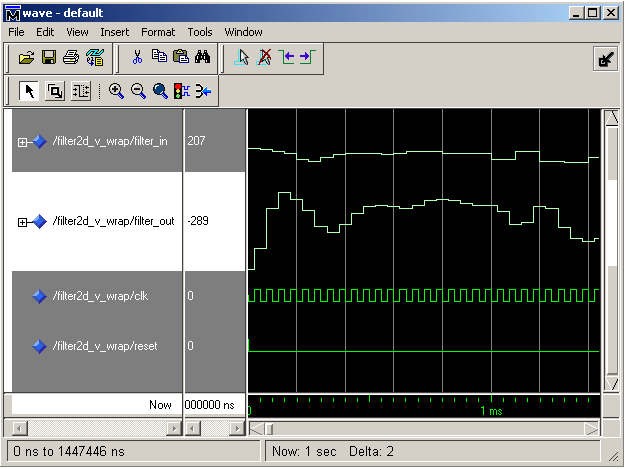

的ModelSim / QuestaSim

指VHDL模型要么Verilog的模型看到HDL验证如何用于协同仿真的Simulink和ModelSim。万博1manbetx最后图显示信号的快照显示的ModelSim。

精辟/ Xcelium参考Verilog的模型了解如何使用HDL验证器软件协同模拟Simulink和Incisive平台。万博1manbetx