从Simulink测试台生成SystemVerilog断言万博1manbetx

新闻部断言块检查其输入信号是否为零。使用这个块来检查你的Simulink万博1manbetx®通过创建布尔表达式并将其连接到块,测试台的行为符合预期。生成SystemVerilog会在生成的模块中创建即时断言。使用此块检查刺激在Simulink和SystemVerilog环境中的行为是否符合预期。万博1manbetx

生成断言工作流

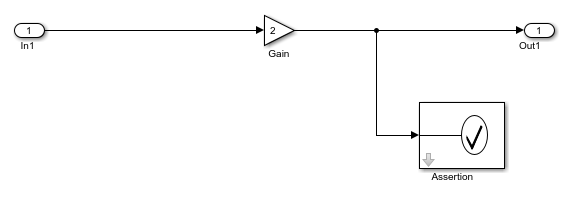

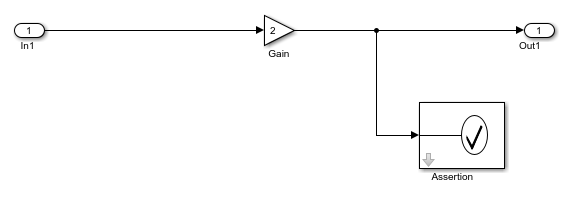

此示例演示如何使用断言块创建模型,断言块在增益块的输出为零时发出警告。然后使用计数器显示模型输出。

创建一个Simul万博1manbetxink模型

示例模型有一个增益块。这个示例在每次增益输出为零时创建一个警告。

打开万博1manbetxSimulink块库>常用砌块.

添加轮廓尺寸块

双击此块以打开其参数。设置的值获得到

2..添加外港块

如上图所示连接所有块。

添加和配置断言块

找到断言阻塞库通过选择HDL验证器>与DPI-C SystemVerilog一起使用.将此块添加到模型中,然后将Gain块的输出连接到断言块的输入。

此示例使用断言块以监视增益输出,并在信号为零时返回警告。双击断言块来配置其参数。设置严重程度到

警告和断言失败的消息到“输出为0!”. 确保启用断言被选中。

注

这个参数节控制Simulink的执行,它们与Si万博1manbetxmulink中的参数相同断言(万博1manbetxSimulink)块这个DPI-C断言选项仅在生成的SystemVerilog中控制断言行为。

自定义断言

通过设置严重程度到

习俗并在断言自定义命令盒子。该命令可以包括系统任务,例如显示美元或$time.您可以使用生成的断言行为进一步定制

DPI_getAssertionInfo (obj)SystemVerilog函数。此函数用于检查执行的断言,并返回SystemVerilog结构数组中为该断言记录的所有信息。对于在该时钟周期中执行的每个断言,函数返回地位,消息,严重程度对断言的解释。在Simulink中运行仿真万博1manbetx

在进行模拟之前,将一个刺激源和一个接收器连接到你的子系统。本例使用一个计数器生成0-1-2-3序列。

要生成并运行模拟,请单击跑工具栏上的按钮。

注意输出中断言块的警告。

生成SystemVerilog DPI组件

在Simuli万博1manbetxnk上应用程序选项卡单击HDL验证器.然后,在HDL验证器选项卡,单击C代码设置.这个配置参数对话框在上打开代码生成.

在系统目标文件,点击浏览选择

systemverilog_dpi_grt.tlc.如果你有嵌入式编码器的许可证®,可选择目标

systemverilog_dpi_ert.tlc. 此目标允许您访问其其他代码生成选项(在模型配置参数的“代码生成”窗格上)。

在代码生成组中,单击SystemVerilog DPI.

要启用自动测试台生成,请选择生成测试台复选框。

点击好吧以接受这些设置并关闭“配置参数”对话框。

上HDL验证器选项卡,单击生成DPI组件.

在“构建子系统代码”对话框中,单击构建.

SystemVerilog组件生成为

dut_构建/dut_dpi.sv在当前工作文件夹中。此外,包含函数声明的包文件在as中生成dut_构建/dut_dpi_包装sv在当前工作文件夹中。

运行SystemVerilog仿真

在HDL验证器选项卡单击选择模拟器打开“配置参数”界面SystemVerilog DPI窗格.然后,从高密度脂蛋白模拟器列表。点击好吧.

要在GUI模式下启动模拟器,请展开运行Testbench按钮并选择在GUI模式下启动模拟器.

在ModelSim®或者,®,输入以下命令启动模拟。

是否运行_tb_mq.do

注意断言显示的模拟警告:

运行-all # ** Warning: assertion:14:output is 0!#时间:40ns作用域:dut_dpi_tb。u_dut_dpi文件:. . / dut_dpi。sv Line: 57 # ** Warning: assertion:14:output is 0!#时间:80ns作用域:dut_dpi_tb。u_dut_dpi文件:. . / dut_dpi。sv Line: 57 # ** Warning: assertion:14:output is 0!#时间:120ns范围:dut_dpi_tb。u_dut_dpi文件:. . / dut_dpi。sv Line: 57 # ** Warning: assertion:14:output is 0!#时间:160 ns作用域:dut_dpi_tb。u_dut_dpi文件:. . / dut_dpi。sv Line: 57 # ** Warning: assertion:14:output is 0!#时间:200ns范围:dut_dpi_tb。u_dut_dpi文件:. . / dut_dpi。sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 240 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 280 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 320 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 360 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 400 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 440 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 480 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # ** Warning: assertion:14:output is 0! # Time: 520 ns Scope: dut_dpi_tb.u_dut_dpi File: ../dut_dpi.sv Line: 57 # **************TEST COMPLETED (PASSED)************** # ** Note: $finish : ./dut_dpi_tb.sv(62) # Time: 542 ns Iteration: 0 Instance: /dut_dpi_tb # End time: 14:16:43 on Dec 29,2017, Elapsed time: 0:00:04 # Errors: 0, Warnings: 13

跟踪生成的SystemVerilog断言

在使用生成的断言运行SystemVerilog模拟之后,日志文件将显示警告和错误。要识别哪个断言块产生了特定的警告或错误输出,请使用hilite_系统(万博1manbetxSimulink)功能。

每个警告显示一个数字,标识具体断言生成该警告的块。该数字是该块的Simulink标识符(SID)。例如,下面显示了由SID号为14的断言块生成万博1manbetx的警告。

#**警告:断言:14:输出为0!

要突出显示生成此警告的块,请在MATLAB中执行以下代码®命令窗口。

hilite_系统(“断言:14”)

有关Simulink标识符的更多信息,请参阅万博1manbetx万博1manbetx动态仿真模块标识符(万博1manbetxSimulink).

禁用断言

您可以禁止在Simulink环境或SystemVerilog环境中执行任何断言块。如果希望在Simulink和SystemVeril万博1manbetxog中忽略断言,请禁用Simulink中的断言。如果不希望从Simulink重新生成代码,但希望能够在SystemVerilog模拟期间禁用断言,请禁用SystemVerilog中的断言。

禁用断言在万博1manbetx.您可以禁用DPI-C断言通过清除启用断言复选框中的断言块参数。

清除此复选框将禁止断言发出任何警告或错误并生成SystemVerilog断言。

禁用SystemVerilog中的断言。在SystemVerilog环境中,您可以通过将Simulink Identifier作为命令行参数提供给HDL模拟器来禁用断言。万博1manbetx例如,当使用ModelSim并假设SID为14时,可以禁用由断言用下面的加参数阻塞:

Vsim -c -voptargs=+acc -sv_lib ../ dut_win64工作。dut_dpi_tb +断言:14

另见

相关的话题

- 万博1manbetx动态仿真模块标识符(万博1manbetxSimulink)

- 生成SystemVerilog DPI组件