SystemVerilog DPI测试台

HDL Verifier™提供两种类型的测试台,可以生成C语言组件,并将其集成到SystemVerilog测试台中,使用直接编程接口(DPI)。一个测试台验证生成的C组件是否来自Simulink的已保存的数据向量万博1manbetx®子系统。另一个测试平台根据从整个Simulink模型生成的C组件验证生成的HDL代码。万博1manbetx

组件测试台——当您从Simulink子系统生成C组件用作DPI组件时,您可以选择生成SystemVerilog测试台。万博1manbetx测试台根据来自Simulink模型的数据向量验证生成的DPI组件。万博1manbetx下面的“模型配置参数”对话框中有此特性代码生成.看生成SystemVerilog DPI组件.

HDL代码测试台 - 当您使用HDL Coder™从子系统生成HDL代码时,您可以选择生成SystemVerilog测试台。该测试台与Simulink模型的结果进行比较HDL实现的输出。万博1manbetx您可以在HDL Workflow Advisor下访问此功能HDL代码生成>设置测试台选项,或在“模型配置参数”对话框中,在HDL代码生成>试验台.或者,对于命令行访问,设置

生成vdpitestbench.的属性makehdltb(高密度脂蛋白编码器).看使用SystemVerilog DPI测试台验证HDL设计(高密度脂蛋白编码器).

两种类型的测试台都需要一个万博1manbetx仿真软件编码器™执照。

限制

HDL验证器在SystemVerilog中将矩阵和向量转换为一维数组。例如,Simulink中的4 × 2矩阵在SystemVeril万博1manbetxog中被转换为一个由8个元素组成的一维数组。

这些子系统不支持DPI测试台生成:万博1manbetx

触发子系统

启用子系统

子系统与动作端口

组件测试台

SystemVerilog DPI组件生成器还创建了测试台。您可以使用此测试台来验证生成的SystemVerilog组件是否在功能上等同于原始Simulink子系统。万博1manbetx测试台从Simulink仿真中保存数据向量以施用为刺激并检查组件的输出。万博1manbetx此测试台并不旨在作为您自己应用程序的系统测试台的替代品。但是,您可以使用生成的测试台作为您自己的系统测试台的起始示例。

如果在模型中启用日志记录测试点,则生成的测试台也将其在SystemVerilog组件中的信号值与Simulink的记录值进行比较。万博1manbetx

笔记

HDL验证者不支持用于自定义生成的Syste万博1manbetxmVerilog代码的测试台生成。看定制.

多速率组件测试台

当子系统包含具有多个采样率的信号时,生成的测试台包括定时控制器模块。定时控制器以适当的速率生成输入时钟信号。输入刺激和预期数据输出并根据其采样率进行检查。

HDL代码测试台

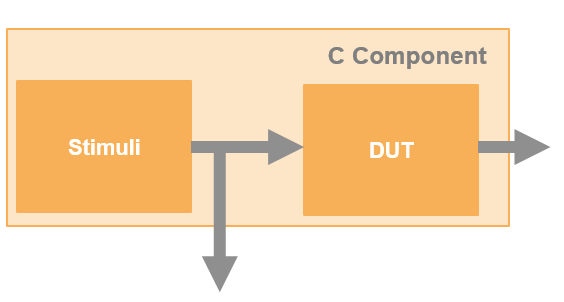

当您使用HDL编码器生成子系统的HDL代码时,您还可以生成SystemVerilog DPI测试台。该测试台与Simulink模型的结果进行比较HDL实现的输出。万博1manbetx除CUT子系统的C代码外,编码器还为模型的部分生成C代码,用于生成输入刺激。该测试台的生成比大型数据集的默认HDL测试台更快。这种优点是因为编码器不运行Simulink模型以获得输入和输出数据向量。万博1manbetx生成的C组件计算输入刺激和输出结果,以便与HDL实现进行比较。

生成的SystemVerilog测试台包括:

生成的Verilog.®或vhdl.®子系统的代码

生成C组件

将HDL代码的输出与C组件的输出进行比较。

运行此测试台以验证生成的HDL代码实现了与您的Simulink模型相同的算法。万博1manbetx