开始自定义生成的SystemVerilog代码

本例向您展示如何在SystemVerilog DPI组件生成过程中自定义生成的SystemVerilog代码。

要求和前提条件

s manbetx 845本例所需的产品:

MATLAB®

万博1manbetx仿真软件®

万博1manbetx仿真软件编码器™

Mentor Graphics®ModelSim®/QuestaSim®

支持的C编译器之一:M万博1manbetxicrosoft®Visual c++或GNU GCC

背景

如果默认生成的SystemVerilog代码不满足您的需求,您可以自定义生成的代码。这个例子展示了如何定制生成的代码。

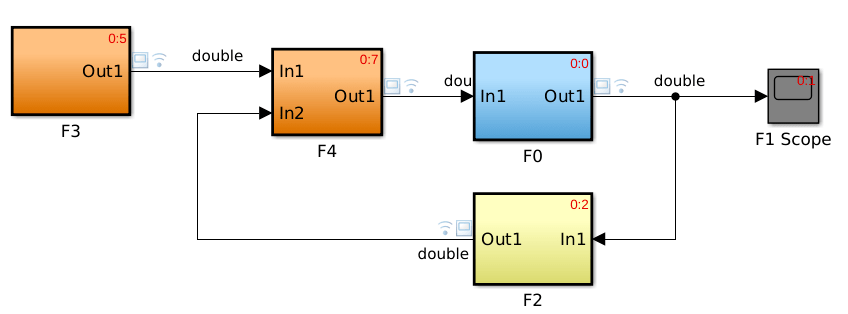

在下面的Simulink模型中,生万博1manbetx成的对应于子系统F0、F2、F3和F4的代码分别作为SystemVerilog模块导出。默认情况下,每个模块包含三个控制信号:clock、clock enable和reset。在HDL仿真中,子系统更新和输出函数将在时钟信号的上升沿被调用。事件调度器将在HDL模拟器中以与Simulink模型相同的顺序触发这些更新和输出函数。万博1manbetx

开放的例子

运行以下代码打开设计

open_system (“svdpi_SimpleFeedBack”);

建立代码生成模型

从svpid_Si万博1manbetxmpleFeedBack模型打开Simulink模型配置参数面板。设置如下参数:

选择“代码生成->系统目标文件”。点击浏览按钮,选择“systemverilog_dpi_grt.tlc”。

在工具链设置中,如果您使用的是Windows,则选择一个Visual Studio版本,如果使用的是Linux,则选择一个GCC工具链。确保“仅生成代码”选项未选中。

选择“Code Generation -> SystemVerilog DPI”,勾选“Customize generated SystemVerilog Code”选项。确保“源文件模板”设置为默认模板“svdpi_event.vgt”。

您也可以单击“编辑”按钮查看默认的SystemVerilog模板。

现在我们已经完成了Configuration Parameter面板。点击“确定”按钮关闭。

生成SystemVerilog DPI组件

在“svdpi_SimpleFeedBack”模型中,为子系统F0、F2、F3和F4生成C代码。在MATLAB中运行以下命令可以从命令行生成C代码:

slbuild (“svdpi_SimpleFeedBack / F0”) slbuild (“svdpi_SimpleFeedBack / F2”) slbuild (' svdpi_SimpleFeedBack / F3 ') slbuild (“svdpi_SimpleFeedBack / F4”)

现在,这些子系统的C代码分别生成在子目录“F0_build”、“F2_build”、“F3_build”和“F4_build”中。

测试台架文件

在测试台中"SimpleFeedback_tb. txt "sv”连接控制信号,使其从Simulink中执行顺序高的模块流向Simulink中执行顺序低的模块。万博1manbetx

运行生成的测试平台

在GUI模式下启动ModelSim/QuestaSim,在MATLAB中将目录更改为当前目录。在ModelSim/QuestaSim中,输入以下命令来编译设计

做build.do

在ModelSim/QuestaSim中,输入以下命令来模拟您的设计

做sim.do

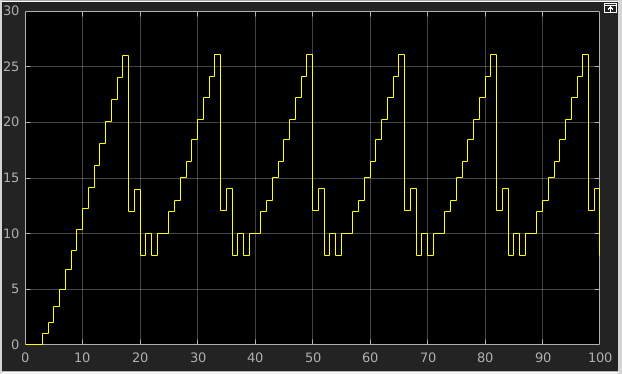

当模拟完成时,您可以检查每个子系统的输出与ModelSim的波形窗口中捕获的信号之间的差异。