UVM组件生成概述

UVM组件生成概述

如果你有万博1manbetx®编码员™许可证,您可以从Simulink模型生成通用验证方法(UVM)测试台和其他组件。生成UVM组件可实现从Simulink环境到UVM框架的直接转换。万博1manbetx

HDL验证器™ 使用直接编程接口(DPI)将万博1manbetxSimulink子系统导出为UVM组件内生成的C代码。可以将这些生成的组件集成到现有的UVM环境中。您还可以使用生成的UVM测试台,通过使用详细的HDL设计替换生成的行为DUT来测试HDL DUT。

为UVM组件生成万博1manbetx准备Simulink模型

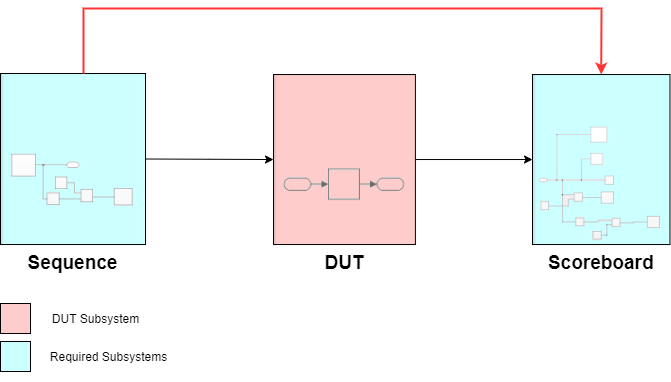

Simul万博1manbetxink模型必须包括这些子系统。

DUT子系统。该子系统生成DUT的SystemVerilog DPI(SVDPI)行为模型。有关SystemVerilog DPI生成的更多信息,请参阅用Simulink生成DPI组件万博1manbetx.

一个序列子系统。这个子系统创建刺激并将其驱动到DUT。

记分板子系统。该子系统收集并检查DUT的输出。

该序列还可以将信号直接驱动到记分板,如Simulink模型结构图中的红色所示。万博1manbetx

创建子系统的详细操作请参见创建子系统(万博1manbetxSimulink).

万博1manbetx仿真软件模型结构

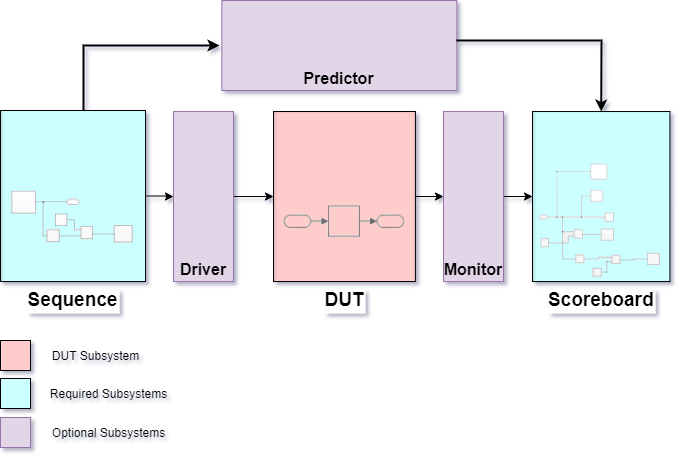

除了前面的结构之外,还可以选择包括这些子系统。

驱动子系统

监控子系统

预测子系统

注

Simulink模型中的所有子系统的名称必须以字母开头万博1manbetx,并使用字母数字字符和下划线的组合。

当添加监视器、驱动程序或预测器子系统时,该特性支持这些配置。万博1manbetx

序列中的所有信号必须连接到驱动器、预测器或记分板。对于UVM生成,忽略其他输出信号。

如果您的模型包含一个驱动子系统,那么所有来自驱动的信号都必须连接到DUT。

如果您的模型包含一个驱动子系统,那么所有给驱动的输入信号都必须在序列中产生。

如果您的型号包括监视器子系统,则来自DUT的所有信号必须连接到监视器。

如果您的模型包括监视器子系统,那么从监视器发出的所有信号都必须连接到记分板。

如果您的模型包含预测器子系统,则预测器的所有输入信号必须源自序列。生成UVM时忽略其他输入。

如果您的模型包含预测器子系统,则预测器的所有输出信号必须连接到记分板。生成UVM时忽略其他输出。

此图显示了一个Simulink模型,其万博1manbetx中包括一个驱动程序、一个监视器和一个预测器子系统。

选择系统目标

因为UVM生成使用了生成SystemVerilog DPI的技术,所以必须首先选择支持系统的目标文件。打开“配置参数”对话框,然后选择万博1manbetx代码生成从左窗格中。对于系统目标文件点击浏览,然后选择systemverilog_dpi_grt.tlc从列表中删除。

或者,如果你有嵌入式编码器®产品,您可以选择目标systemverilog\u dpi\u ert.tlc. 此目标使您能够在选择时访问其他代码生成选项代码生成从“配置参数”对话框的左窗格中。

有关UVM生成的示例,请参见从Simulink生成参数化UVM测试台万博1manbetx.

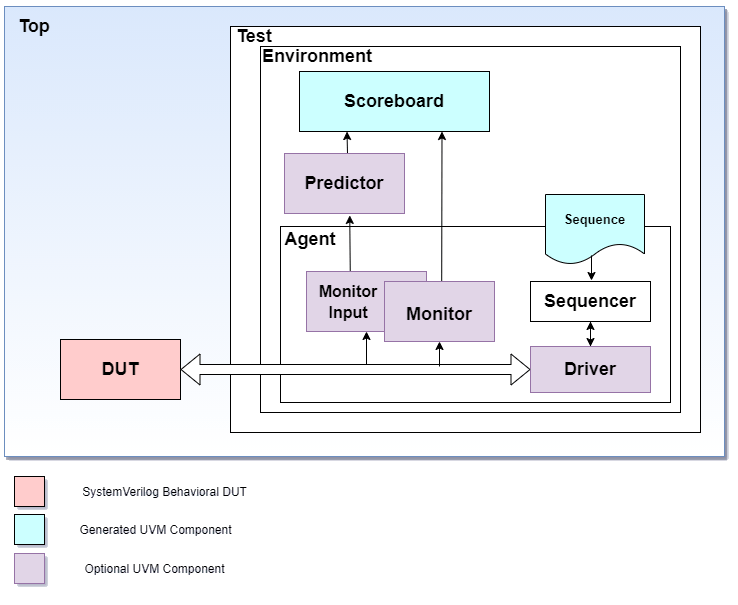

生成UVM结构

使用uvmbuild函数来生成这种UVM组件结构。

Top–此模块实例化生成的行为DUT和测试环境。顶部模块具有传播到设计中的时钟和复位信号。

DUT–从Simulink DUT子系统生成测试中的行为设计模块。万博1manbetx

测试–此模块包括UVM环境和序列类。

序列–此UVM对象定义一组事务。序列对象是从Simulink序列子系统生成的。万博1manbetx

环境–此模块包括代理和生成的记分板,以及可选的预测器。

记分板–UVM记分板是从Simulink记分板子系统生成的。记分板将预期结果与DUT的输出进行比较。万博1manbetx

代理—UVM代理包括音序器、驱动程序和监视器。如果存在从Simulink序列子系统到Simulink记分牌子系统万博1manbetx的直接路径,则包含一个附加的监视器(如图中红色部分所示)来监视该信号。

该模块控制到DUT的序列事务流。

Driver -该模块由Simulink驱动子系统生成,并将每个事务从序列转换为行为DU万博1manbetxT理解的信号。

监视器–此模块由Simulink监视器子系统生成,它对来自行为DUT的信号进行采样,并生成万博1manbetx发送到UVM记分板的事务。

Monitor Input—如果您有一个预测器或从序列到记分牌子系统的直接连接,则会生成此模块。监视器输入对序列中的信号进行采样,并生成发送到UVM预测器或记分牌的事务。

这个模块是从你的Simulink预测器子系统中生成的。万博1manbetx预测器代表了DUT的黄金模型。它从序列中接收输入,计算结果,并将结果驱动到计分板以与DUT结果进行比较。

有关UVM组件和结构的详细信息,请参见UVM参考指南.

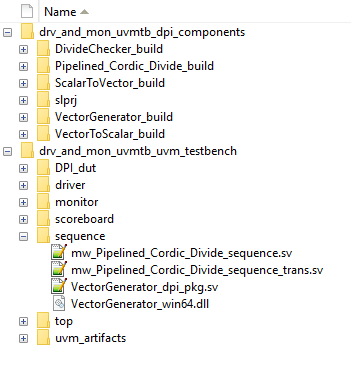

生成的文件和文件夹结构

生成UVM组件时,HDL Verifier从DUT、序列和记分板子系统生成SystemVerilog DPI(SV-DPI)组件,以及驱动器、监视器或预测器子系统的可选SV-DPI组件(如果模型包含)。DPI生成的工件放置在名为uvm_建筑在您的工作目录中,包括以下两个目录:

托普模型_dpi_组件托普模型_uvm_试验台

哪里托普模型构建目录房地产uvmcodegen.uvmconfig配置对象。

这个托普模型_dpi_组件子系统_建造

子系统_dpi_pkg.sv子系统_dpi.sv扩展名为.c和.h的DPI组件和头文件

扩展名为.mat、.txt、.dmr、.tmw和.def的元数据和信息文件

用于将组件编译为.o和.so文件的makefile

这个托普模型_uvm_试验台

DPI_dut-该文件夹包含SystemVerilog包、模块文件和。dll文件的副本dut_建造司机(可选)–如果您将驱动程序子系统指定给uvmbuild函数。该文件夹包含UVM驱动程序、SystemVerilog包的副本和来自司机_建造班长(可选)–如果您将监控器子系统指定给uvmbuild功能。此文件夹包含一个UVM监视器、一个SystemVerilog软件包的副本以及来自的共享库文件(dll文件或so文件)班长_建造预测(可选)–如果您将预测器子系统指定给uvmbuild函数。该文件夹包含一个UVM预测器、一个SystemVerilog包的副本、一个预测器事务和来自预测_建造记分牌-该文件夹包含SystemVerilog包的副本和。dll文件记分牌_建造序列-该文件夹包含SystemVerilog包的副本和。dll文件序列_建造顶部–此文件夹包含顶级Simulink型号的SystemVerilog软件包和模块文件。此文件夹还包含用于HDL模拟器执行的脚本。万博1manbetxuvm_artifacts–此文件夹包含这些SystemVerilog文件。mw_–此文件包括一个UVM代理,用于实例化序列、驱动程序和监视器。DUT_agent.svmw_–该文件包括一个UVM环境,它实例化了一个代理和一个记分板。DUT_environment.svmw_–该文件定义DUT SystemVerilog接口类型。它包含DUT输入和输出,以及用于时钟、复位和时钟启用信号的端口。DUT_if.svmw_–该文件包括一个直通式UVM监视器。监视器从驾驶员向记分板或预测器采集信号。DUT_monitor_input.svmw_-这个文件包括一个UVM测试,它实例化一个环境和序列。测试模块通过调用来启动事务DUT_test.sv顺序:开始.mw_dpi_types_pkg.sv—该文件包含生成的SystemVerilog类型的定义,例如枚举和结构,由UVM组件接口公开。只有使用这些类型的UVM组件才会导入这个包。mw_–默认情况下,此文件包含一个直通UVM驱动程序。将驱动程序子系统指定给DUT_driver.svuvmbuild函数,此模块包括调度程序和对DPI组件的API调用司机_dpi_pkg.svmw_–该文件包括一个直通式UVM监视器。监视器从DUT向记分板采集信号。将监控器子系统指定给DUT_monitor.svuvmbuild函数时,该模块包括一个调度程序和对dpi组件的API调用监控_dpi_pkg.sv

该图像显示了为名为drv_和_mon_uvmtb.

万博1manbetx支持万博1manbetx数据类型

万博1manbetx支持的Simulin万博1manbetxk数据类型转换为SystemVerilog数据类型,如下表所示。

生成的SystemVerilog类型

| MATLAB® | SystemVerilog | ||

|---|---|---|---|

| 兼容的C类型 | 逻辑向量 | 位向量 | |

uint8 |

字节无符号 |

逻辑[7:0] |

位(7:0) |

uint16 |

shortint无符号 |

逻辑[15:0] |

比特[15:0] |

uint32 |

整数无符号 |

逻辑(31:0) |

比特[31:0] |

uint64 |

longint无符号 |

逻辑(63:0) |

位(63:0) |

int8 |

字节 |

逻辑签名[7:0] |

位签署(7:0) |

int16 |

shortint |

逻辑(15:0)签署 |

位符号[15:0] |

int32 |

int |

逻辑签名[31:0] |

位签署(31:0) |

int64 |

长整型 |

逻辑(63:0)签署 |

位符号[63:0] |

布尔 |

字节无符号 |

逻辑0时 |

位(0时) |

| 定点 | 端口符号扩展为内置C类型,例如 |

逻辑向量长度( |

位向量长度( |

单 |

短波雷亚尔 |

||

双重的 |

真正的 |

||

复杂的 |

您可以选择SystemVerilog |

||

| 向量,矩阵 | 您可以在SystemVerilog阵列或标量端口之间进行选择。要在这些选项之间进行选择,请在“配置参数”对话框的左窗格中选择代码生成>SystemVerilog DPI,然后选择标量化矩阵和向量端口参数 例如,一个两元素类型的向量 输入逻辑[31:0] 当您选择标量化矩阵和向量端口,生成的SystemVerilog包括这两个端口,每种类型 输入逻辑[31:0]vecInput\u 0,输入逻辑[31:0]vecInput\u 1 生成向量和数组端口时,编码器按列主顺序展平矩阵。 |

||

| nonvirtual总线 | 您可以选择SystemVerilog |

||

| 枚举数据类型 | 枚举 |

||

限制

默认情况下,HDL验证器在SystemVerilog中将矩阵和向量转换为一维数组。例如,Simulink中的4 × 2矩阵在SystemVeril万博1manbetxog中被转换为一个由8个元素组成的一维数组。要在SystemVerilog接口中生成多个标量端口,请选择标量化矩阵和向量端口在配置参数中。

这个

uvmbuild函数忽略未指定为DUT、序列、记分万博1manbetx板、驱动器、监视器或预测器子系统的Simulink组件。您可以在任何子系统内部使用反馈回路,但不能在它们之间使用。

序列、记分板和预测子系统必须以单一的速率运行,并且它们的子系统的基本采样时间必须相等。有关示例时间的更多信息,请参见系统中的采样时间(万博1manbetxSimulink).

驱动、DUT和监控子系统的基本采样时间必须相等。它们的端口可以是多速率的,但最大公约数(GCD)或基本采样时间必须相同。

序列、记分板和预测器子系统的采样时间必须大于或等于驾驶员、DUT和监视器的基本采样时间。