使用状态流设计和评估连续近似ADC

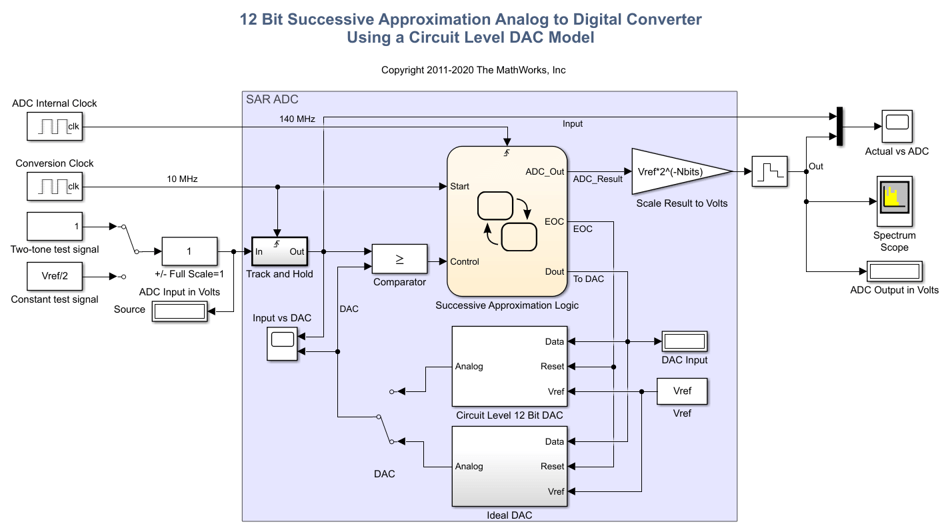

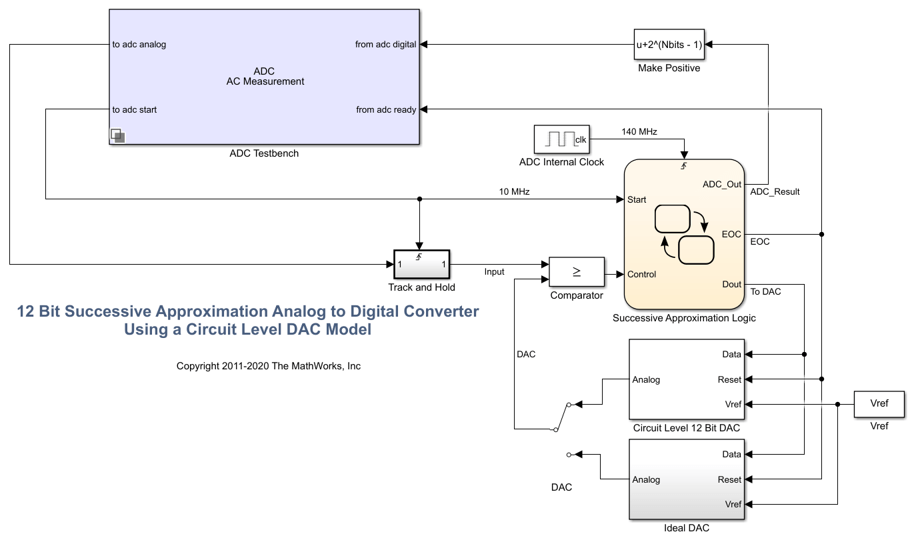

这个例子展示了一个带有电路级DAC模型的12位逐次逼近寄存器(SAR) ADC。

连续的近似ADC通常具有12到16位分辨率,并且它们的采样率范围为10 ksamples / sec至10 msamples / sec。它们往往会花费较低,并且比分别ADC少得更少。

模型

打开系统MSADCSuccessiveApproximation.

模型=“MSADCSuccessiveApproximation”;Open_System(型号)

将交换机设置为默认位置,选择双音源和理想的DAC模型。

set_param([模型“/源”],“西南”,' 1 ');set_param([模型'/ dac'],“西南”,' 0 ');

顶级模型由Testbench和正在测试的设备组成。测试窗包括测试信号发生器和时域范围和频谱分析仪,用于测量目的。在模型中以蓝色突出显示的已测试设备包含轨道和保存:,比较器,控制逻辑和充电缩放DAC。

测试信号是双音正弦波或恒定直流电平输入。这个测试信号被采样并保持在ADC的输出字率为10兆赫。采样器的输出作为比较器的一个输入。第二个比较器输入是DAC输出,它是一个渐进的阶梯参考电平。如果采样器的输出大于或等于DAC输出,那么比较器输出逻辑1。当这种情况发生时,相应的输出位被设置为逻辑1。否则,比较器输出一个逻辑0,它不增加ADC输出字。这个单一的比较器只是在逐次逼近转换器中,模拟被转换成数字。

sim(模型);

定义位数(NBits)和ADC转换率(FS.)在Matlab®工作区中。ADC操作时钟速率取决于Nbits和FS..

nbits = 12;FS = 1E7;adc_clock = fs *(nbits + 2);

连续近似控制逻辑

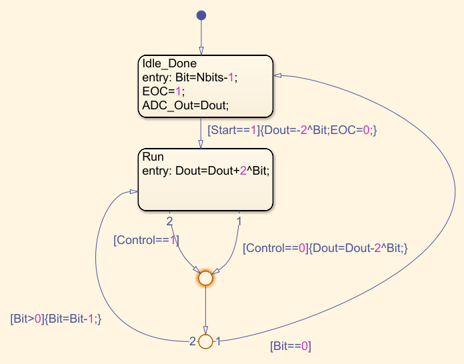

此模型使用StateFlow来模拟连续近似控制逻辑。状态机用作序列器,其通过输出与MIDSCALE对应的计数来开始,这在这种情况下是0伏。然后,状态机器一次执行一个比特位置的二进制搜索,以找到与在分辨率的12位内的采样输入信号相对应的计数。

Open_System([模型'/连续近似逻辑'],'力量')

在一个特定的位上,如果比较器输出1,则设置该位。否则该位位置将被清除。因为有12位,在比特率时钟下需要12个时钟周期来完成给定输入样本的转换。

在这个模型中,由块标记的ADC内部时钟表示的比特率时钟运行在140MHz。这个时钟比模型左上角标记为Conversion clock的块所表示的采样率时钟快14倍。在从第11位到第0位的控制逻辑序列之后,转换结束(EOC)线走高,告诉DAC电路复位。

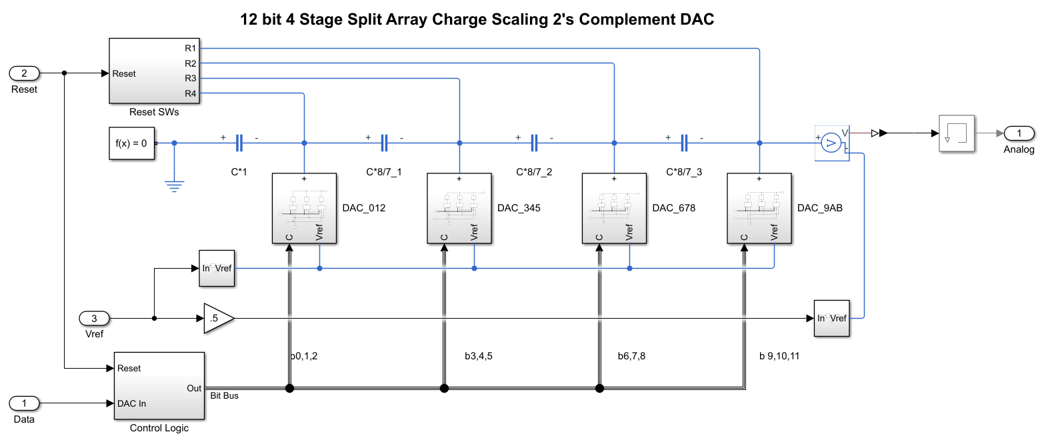

DAC电路级实现

电路级DAC采用分段阵列格式的多级充电比例电容器阵列。这种结构提供了几个优点,包括减少面积或部件数量,内置采样和保持,低功耗,以及在没有分裂阵列的情况下所需的相对较小的电容值范围。

在这个模型中有两个版本的数模转换器(DAC),一个在电路级,第二个代表理想的DAC行为。理想的DAC块接受输入计数并将其乘以

![$$ \ frac {v_ {ref}} {2 ^ {n_ {bits}}} = \ frac {2 \ sqrt {2}} {2 ^ {12}} \ left [\ frac {volts} {count}右] $$](http://www.tianjin-qmedu.com/help/examples/msblks/win64/SuccessiveApproximationADCExample_eq08430490969459080175.png)

以产生输出比较电压[1]。

设置开关以启用电路级DAC模型。运行模型。

set_param([模型'/ dac'],“西南”,' 1 ');sim(模型);

此特定的充电缩放阵列使用 每级的二加权电容总数为

每级的二加权电容总数为 提供总共的阶段

提供总共的阶段 DAC分辨率的位。每级的二值加权电容值为

DAC分辨率的位。每级的二值加权电容值为 ,

, , 和

, 和 .电容越大,对应于特定级中的较高位元位置。例如,设置低侧

.电容越大,对应于特定级中的较高位元位置。例如,设置低侧 电容高有4倍的输出电压冲击相对设置的低侧

电容高有4倍的输出电压冲击相对设置的低侧 电容器高。

电容器高。

如果更改变量的值Nbits,转换器的物理位数,需要修改DAC的电路电平实现。理想的DAC实现和控制逻辑是根据比特数来参数化的。

Open_System([模型'/电路级别12位DAC'],'力量')

每个阶段都由具有值的缩放电容分隔 .缩放电容器的作用是衰减各级输出电压的输出电压。这个阶段离DAC输出节点越远,衰减就越大。衰减是8x每缩放电容对应

.缩放电容器的作用是衰减各级输出电压的输出电压。这个阶段离DAC输出节点越远,衰减就越大。衰减是8x每缩放电容对应 .

.

三个MSB最接近输出,位0,1和2,而LSB,位10,11和12最远。在任何给定的时间,DAC都是两种模式之一。它是基于特定输入计数产生输出电压,或者当EoC线路高时时它正在复位。当EOC变高时,DAC中的每个电容器的低端切换到地而不是数据,从而将电荷的电容器排出以准备接下来的近似。这有效地排出了对下一个输入样本的电容器电压网络准备它。

测量Testbench

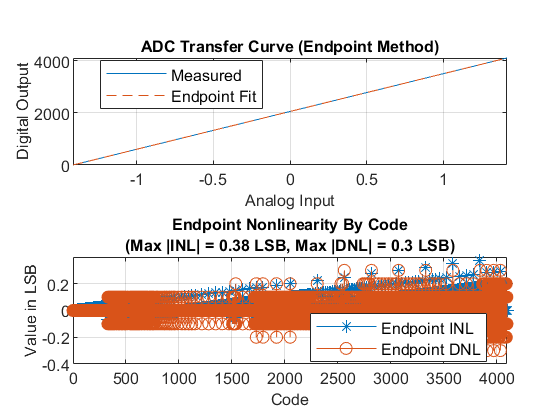

来自混合信号块集™的ADC Testbench块可以提供ADC的性能分析。

在DC模式下,ADC TestBench测试ADC的线性。测试结果用于生成偏移和增益误差测量,这些屏蔽显示在块掩码上。通过ADC TestBench块屏蔽上的按钮可用于导出或可视化的完整测试结果。

bdclose(模型);模型=“MSADCSAR_DC”;Open_System(型号);sim(模型);

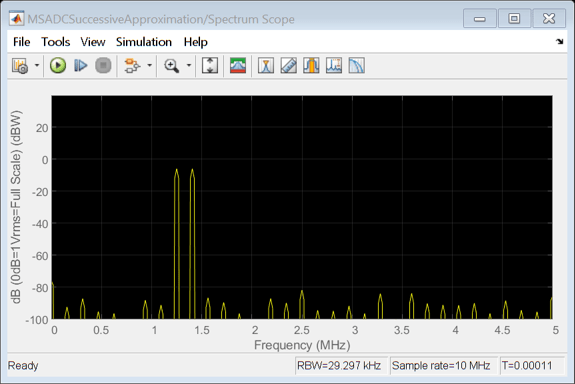

ADC TestBench的AC模式提供了对ADC的频率性能的洞察,包括eNOB(有效位数),最大测量的转换延迟和转换器的噪声底板的测量值。这些测量显示在模拟后的块图标上,可通过块掩码上的按钮导出。

模型='msadcsar_ac';Open_System(型号);set_param([模型'/ dac'],“西南”,' 1 ');

参考

Haideh Khorramabadi UC Berkeley,电气工程系和计算机科学系,第15页,第38页< http://inst.eecs.berkeley.edu/ ~ ee247 / fa06 /讲座/ L15_f06.pdf>

版权所有2019-2020 The MathWorks, Inc。保留所有权利。