使用Simscape高密度脂蛋白工作流顾问

如果您拥有HDL Coder™许可证,您可以使用Simscape HDL Workflow Advisor从Simscape™模型生成HDL代码,以便部署到FPGA平台上。Simscape HDL Workflow Advisor生成Simulink万博1manbetx®Simscape模型的实现然后使用HDL Coder将Simulink模型转换为HDL代码。万博1manbetx将Simscape模型转换为HDL代码可以:

通过使用Simscape模型的优化实现加速物理系统的模拟

快速原型模型使用可重构和并行的FPGA能力

使用硬件在环(HIL)仿真实时模拟HDL实现

基本SimscapeHDL工作流顾问步骤

按照以下步骤,使用Simscape HDL Workflow Advisor将Simscape模型转换为HDL代码。

为Simscape模型生成基线结果。

方法确保模型只包含线性或可切换的线性块

simscape.findNonlinearBlocks函数。确保模型的模拟结果与基线结果相匹配。

为实时仿真和HDL代码生成配置Simscape网络:

添加允许您在模拟时间方面监控HDL工作流的进度的块。

显示样本时间信息。

为固定步长、固定成本模拟配置Simscape网络。

确保离散模型的模拟结果与基线结果相匹配。

控件运行Simscape HDL Workflow Advisor任务

sschdladvisor(高密度脂蛋白编码器)函数。HDL工作流顾问:通过确保模型仅包含线性和切换线性块,并配置为实时模拟,检查HDL代码生成兼容性。

提取Simscape网络的状态空间系数。

生成一个与Simscape网络的HDL代码生成兼容的实现。

确保HDL代码生成兼容实现的模拟结果与基线结果匹配。

生成HDL代码:

运行

hdlsetup(高密度脂蛋白编码器)函数。这个hdlsetup函数配置用于生成HDL代码的固定步长求解器,并指定模拟的启动和停止时间。保存模型参数和验证模型生成设置。

使用

makehdl函数。

在运行Simscape HDL Workflow Advisor之前,配置您的网络以排除:

事件

模式的图表

延迟

启用运行时参数

周期性的来源

由网络连接引起的非线性——如果你的模型确实包含这类非线性,那么

sschdladvisor函数可以运行所有任务直至完成,但会生成一个零值输出。

生成HDL代码Simscape模型使用Simscape高密度脂蛋白工作流顾问

这个示例展示了如何使用Simscape HDL Workflow Advisor将Simscape模型转换为HDL代码。要配置Simscape网络和Simulink模型以进行实时仿真和HDL代码生成万博1manbetx,请参见模型制备.要打开已经准备好使用Simscape HDL Workflow Advisor的模型版本,请参阅使用Simscape HDL工作流顾问生成HDL代码.

模型制备

为FPGA部署准备Simscape模型:

打开

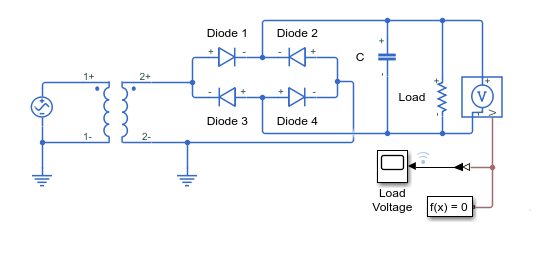

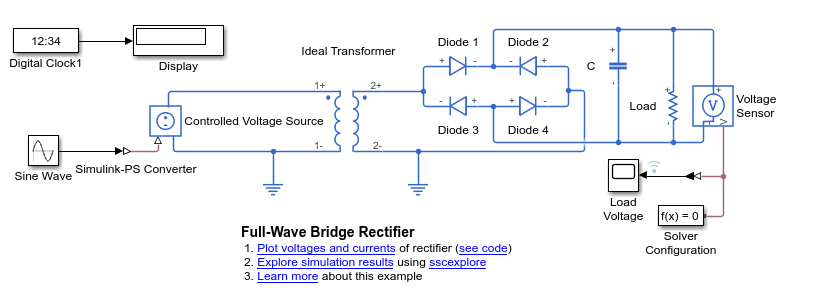

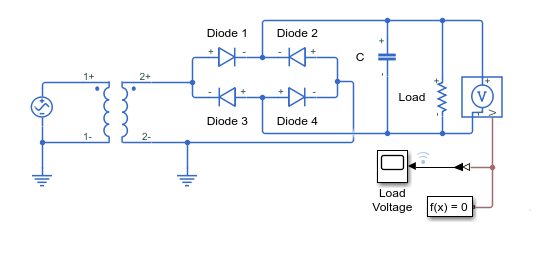

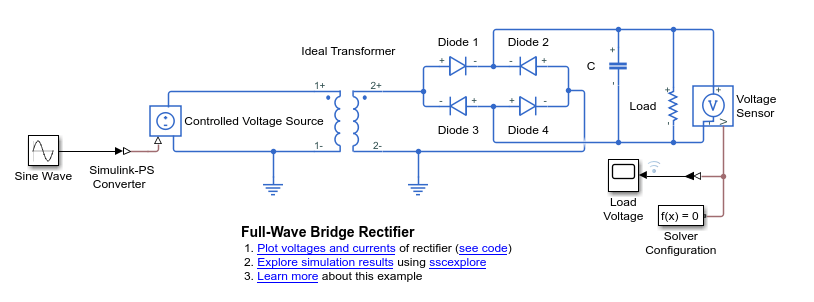

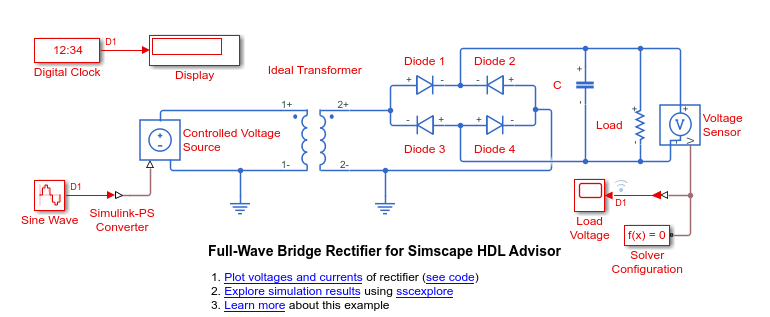

ssc_桥式整流器建模并显示隐藏的块名称。在MATLAB®命令提示符,输入baselineModel =“ssc_桥式整流器”;load_system baselineModel set_param (baselineModel,“HideAutomaticNames”,“关闭”) open_system (baselineModel)

为了将基线模拟结果与后续迭代进行比较,请去掉范围块标记的负载电压范围块,并捕获输入数据的信号范围的仿真数据检查器中启用数据日志记录。

打开范围块。点击视图>配置属性.在日志记录选项卡,明确限制数据点到最后.

控件的连接单击右键范围块,并选择

日志选择信号.日志徽章 出现在信号上方。

出现在信号上方。

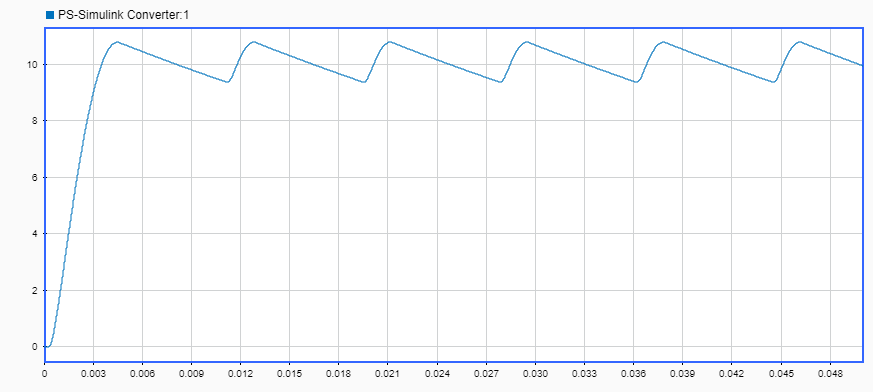

模拟模型并在仿真数据检查器中查看结果。

%%模拟基线模型sim (baselineModel)%%获取模拟数据检查器运行idrunIDs = 万博1manbetxSimulink.sdi.getAllRunIDs;runID = runIDs(结束);运行= Si万博1manbetxmulink.sdi.getRun (runID);signal1 = run.getSignalByIndex (1);% run.signalCountsignal1.checked=true;Sim万博1manbetxulink.sdi.view

根据需要,按键盘上的空格键以适应要查看的模拟数据检查器图。

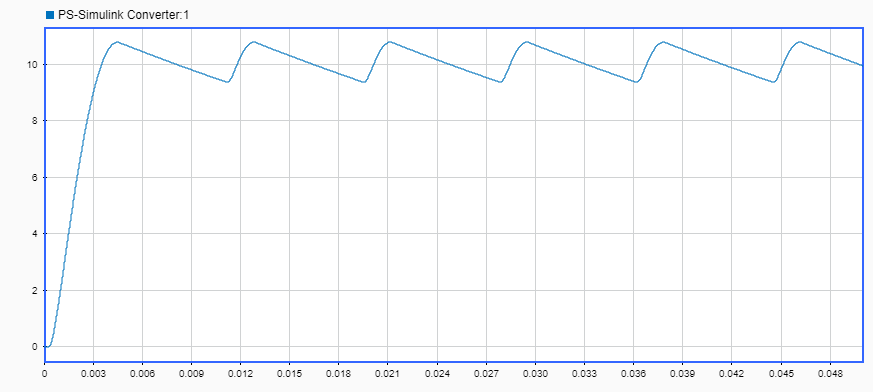

基线仿真返回全波桥式整流负载电压的预期结果。

在运行advisor之前,确定并更换导致网络非线性的块。要识别块,请使用

simcape.findNonlearBlocks函数。simscape.findNonlinearBlocks (baselineModel)

该模型中线性或交换线性网络的数量为0。模型中非线性网络个数为1。ans = 1×1 cell array {'ssc_bridge_rectifier/AC Voltage Source'}该模型包含一个交流电压源块,产生非线性方程的周期源。

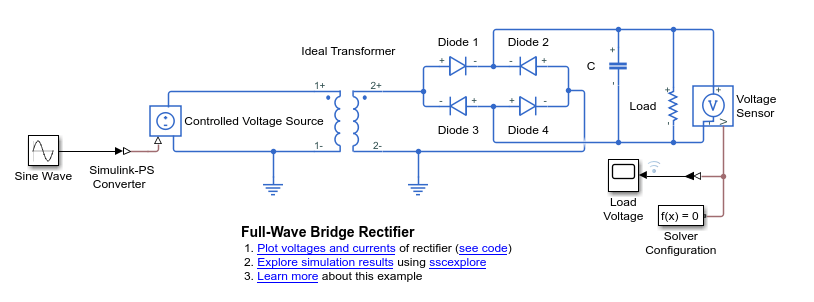

你可以用a代替周期源控制电压源块在Simscape网络中正弦波封锁网络外。

删除交流电压源块。

添加一个正弦波块的万博1manbetx>来源图书馆。

添加一个万博1manbetxSimulink-PS转换器块的Simscape>公用事业公司图书馆。

添加一个控制电压源块的Simscape基础库电电力来源图书馆。

连接正弦波块的万博1manbetxSimulink-PS转换器块和万博1manbetxSimulink-PS转换器块的控制电压源块。

配置正弦波块以匹配交流电压源你移除的块。

设置振幅参数

√2 * 120.设置频率(rad /秒)参数

60 * 2 *π.设置样品时间参数

1 e-5.然后点击三个点图标 旁边的样品时间框,并选择创建变量.变量的名字

旁边的样品时间框,并选择创建变量.变量的名字Ts并点击创建.现在,您可以在工作区中查看和编辑此变量。

确保没有区块导致网络非线性。

%模拟sim (baselineModel)%检查非线性块simscape.findNonlinearBlocks (baselineModel)

模型中线性或交换线性网络的数量为1。Ans = 0×0空单元格数组

该模型只包含生成线性或转换线性方程的块。

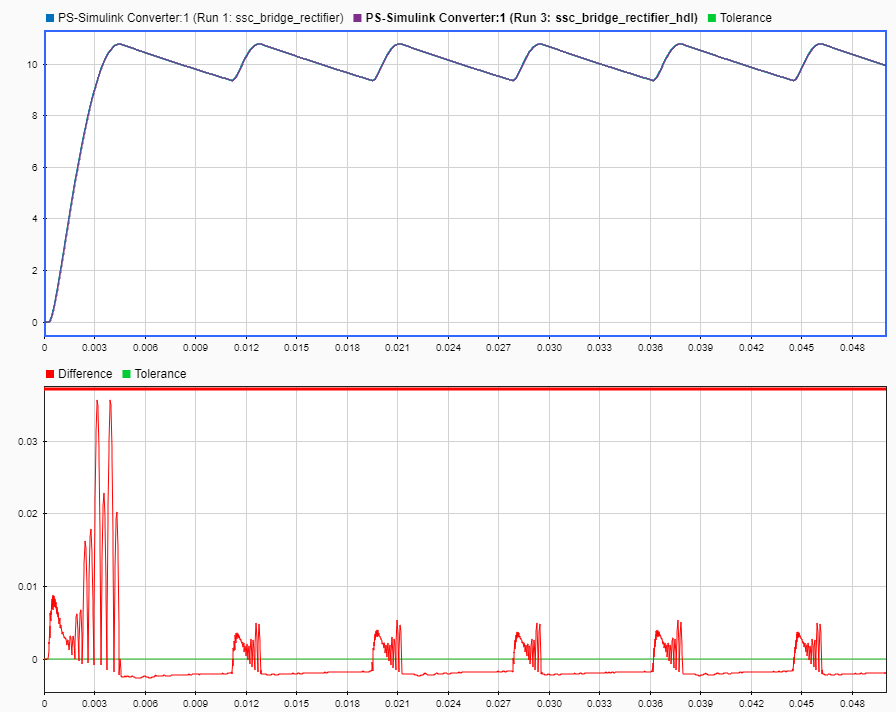

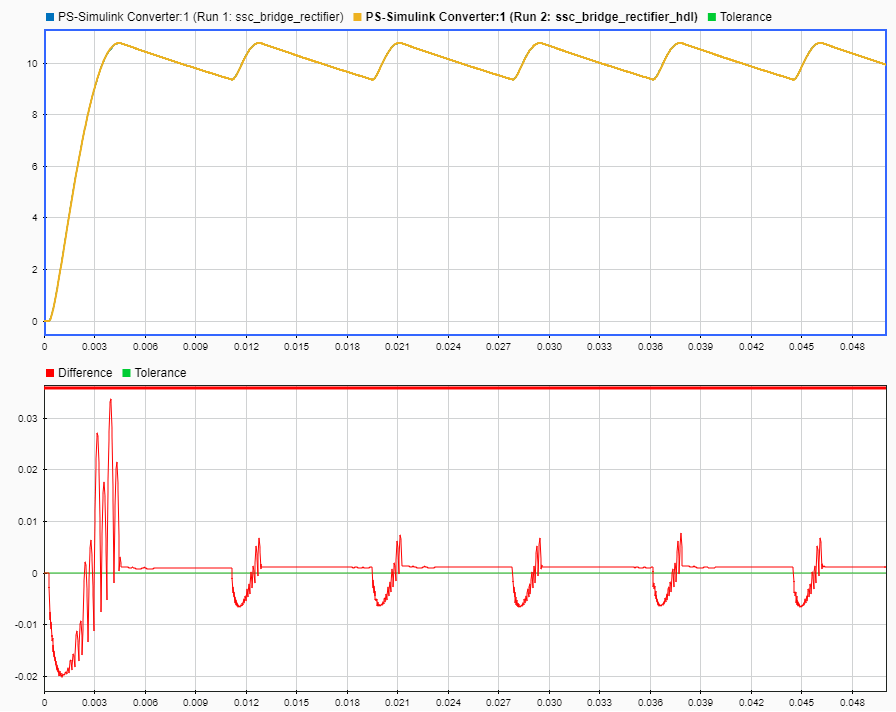

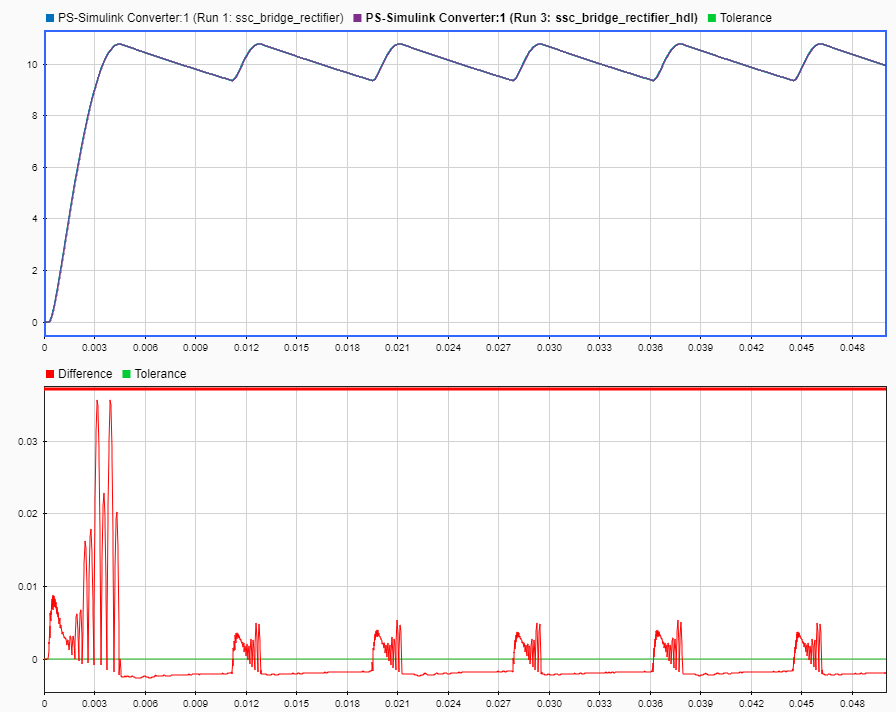

在仿真数据检查器中模拟模型并将结果与基线结果进行比较。

%获取模拟数据检查器运行idrunIDs = 万博1manbetxSimulink.sdi.getAllRunIDs;runBaseline = runid (end - 1); / /结束runSwitchedLinear = runIDs(结束);%打开模拟数据检查器万博1manbetxsimulink .sd .view = simulink .sd . compareruns (runBaseline,...runSwitchedLinear);

结果与基线结果相似。

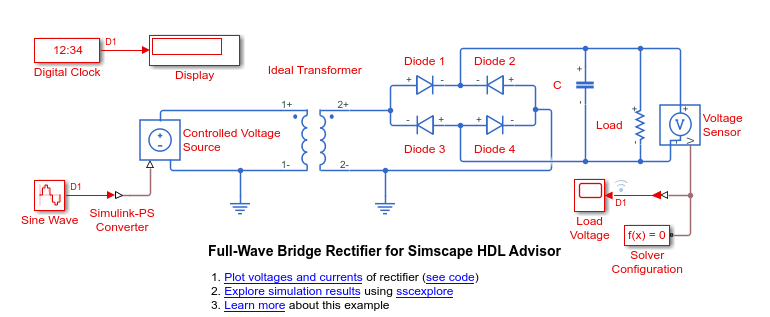

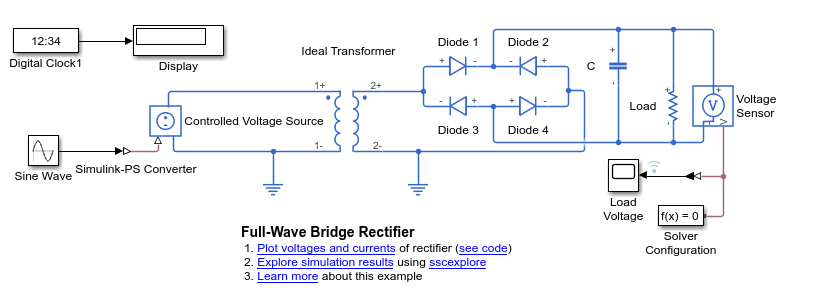

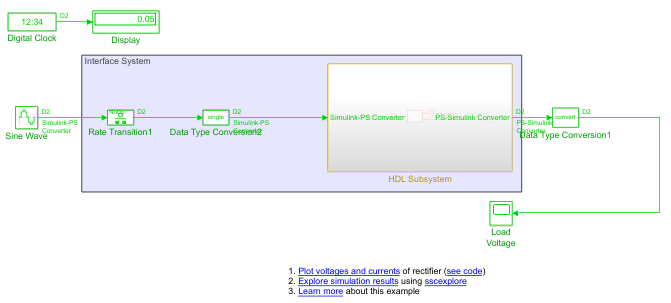

要执行Simscape HDL Workflow Advisor的未来进度检查,请添加并连接一个数字钟块的万博1manbetx>来源图书馆与图书馆显示块的万博1manbetx汇库,如图所示。为数字钟,设置样品时间参数

Ts.

模型仍然设置为使用变步长求解器。对于实时模拟,必须使用固定步长求解器。使用示例时间颜色和注释来帮助您确定模型是否包含任何连续设置。要打开样品时间颜色和注释,在调试选项卡,单击信息覆盖,并在样品时间组,选择颜色和文本.

模型关系图将更新,并显示Timing Legend窗格。

为实时仿真配置模型。

为固定步长、固定成本模拟配置万博1manbetxSimulink模型。在“配置参数”窗口中,单击解算器并设置:

类型来

固定步解算器来

离散(无连续状态)

为固定步长、固定成本模拟配置Simscape网络。为解算器配置区块:

选择使用本地解算器.

确保解算器类型被设置为

向后欧拉.指定

Ts为样品时间.

在仿真数据检查器中模拟模型并将结果与基线结果进行比较。

%模拟sim (baselineModel)%获取模拟数据检查器运行idrunIDs = 万博1manbetxSimulink.sdi.getAllRunIDs;runBaseline = runid (end - 2); / /结束runRealTime = runIDs(结束);%打开模拟数据检查器万博1manbetxsimulink .sd .view = simulink .sd . compareruns (runBaseline,...runRealTime);

结果与基线结果相似。

生成HDL代码使用Simscape高密度脂蛋白工作流顾问

的Simscape模型上运行Simscape HDL Workflow Advisor生成HDL代码模型制备部分或通过打开ssc_bridge_rectifier_hdl模型,它为代码生成做好了准备。

重命名模型。

如果您在模型准备部分中准备了模型,请重命名模型

ssc_model.要打开和使用已经为HDL代码生成准备好的模型,请在MATLAB命令提示符处输入

open_system (“ssc_bridge_rectifier_hdl”)将模型保存到本地目录为

ssc_model.

运行Simscape HDL Workflow Advisor。

sschdladvisor(“ssc_model”)打开Simscape HDL Workflow Advisor。

运行代码生成兼容性检查。

选择代码生成的兼容性>检查解算器配置,然后单击运行这个任务.

选择检查模型的兼容性,然后单击运行这个任务.

当模型通过这些检查时,advisor会报告。

提取状态空间系数。选择状态转换并点击运行所有.转换可能需要一些时间。

运行任务后,advisor将显示状态空间表示形式的摘要和参数表。

状态数:5

输入数量:1

输出数量:1

模式数量:7

微分变量个数:1

离散采样时间:1e-05

参数 参数的大小 A. 5 x 5 x 7 B 5 x 1 x 7 F0 5 x 1 x 7 C 1 x 5 x 1 D 1 x 1 x 1 Y0 1 x 1 x 1 状态、模式和参数数据的大小可以帮助您估计部署模型需要多少FPGA资源。数值越大,需要的FPGA资源越多。输入和输出数据表明了实时部署和可视化所需的I/O连接的数量和类型。

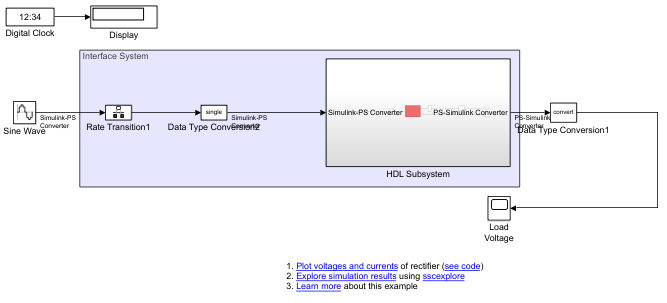

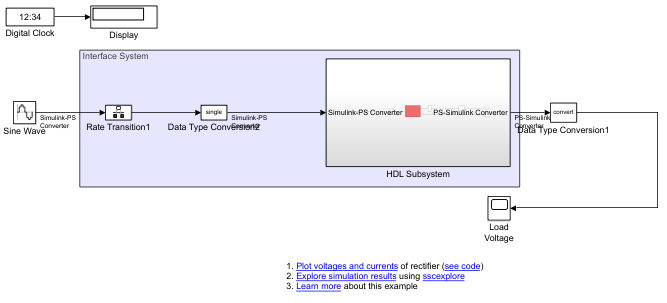

生成模型的HDL实现。选择实现模型的一代>生成实现模型并点击运行这个任务.

当Simscape HDL Workflow Advisor生成实现模型时,该Advisor报告所传递的任务,并显示到生成的实现模型的链接,该实现模型被命名为

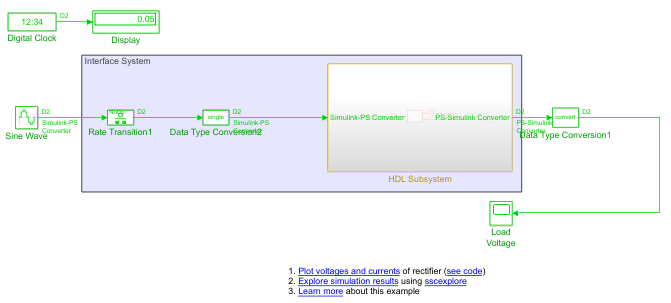

gmStateSpaceHDL_ssc_model.通过单击打开生成的实现模型gmStateSpaceHDL_ssc_model.

该模型包含来自原始模型的块,以及支持HDL Workflow Advisor的新块:万博1manbetx

数字钟,显示,正弦波,负载电压-从您的原始模型的残余

速率转换1 -处理以不同速率操作的块之间的数据传输。

数据类型转换1,数据类型转换2 -在双精度和单精度数据类型之间转换。HDL代码生成需要单精度数据

HDL子系统-包含Simscape网络的HDL代码生成兼容版本。

负载电压,范围显示负载电压的块。

准备与基线结果进行模拟比较的实施模型:

您可以根据需要调整自动生成的模型,并删除残留块,以提高模型的清洁度。这个Digial时钟块和显示块是不必要的,但不会抑制仿真结果。

右键单击Scope块中的输入信号并单击日志选择信号.

这个显示块显示经过的模拟时间。

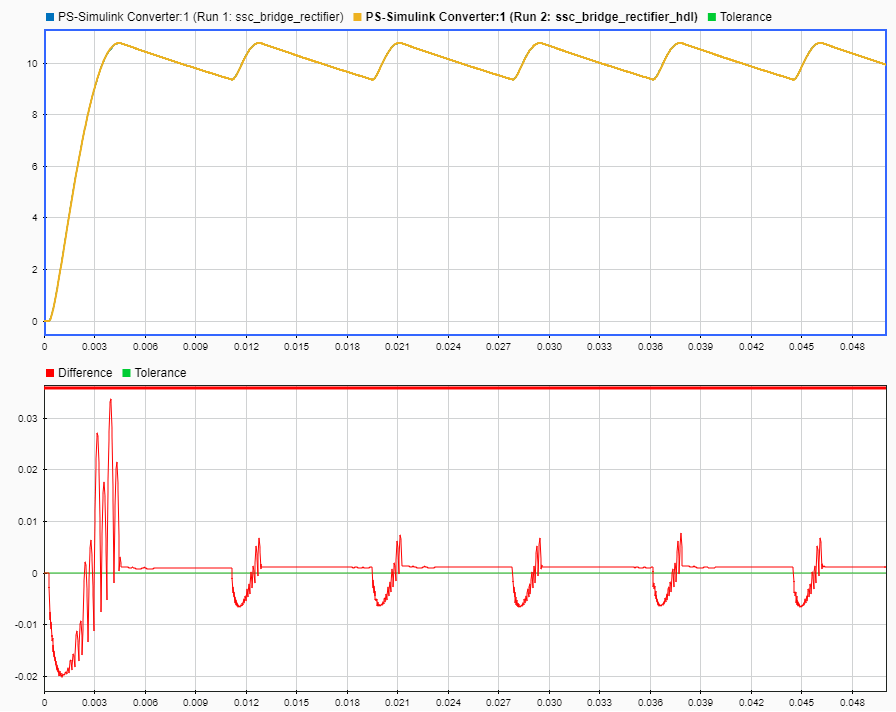

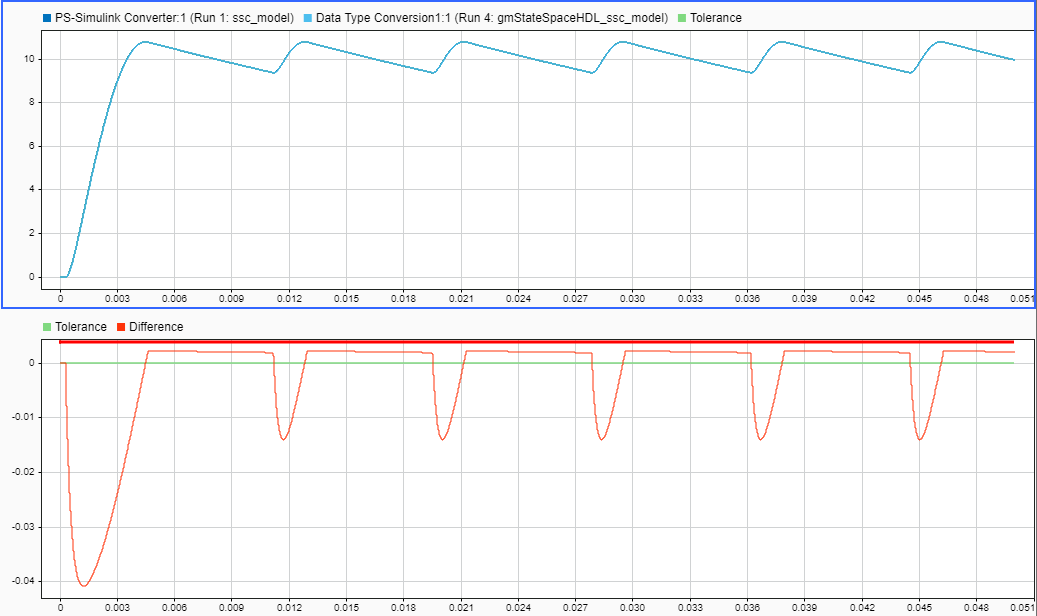

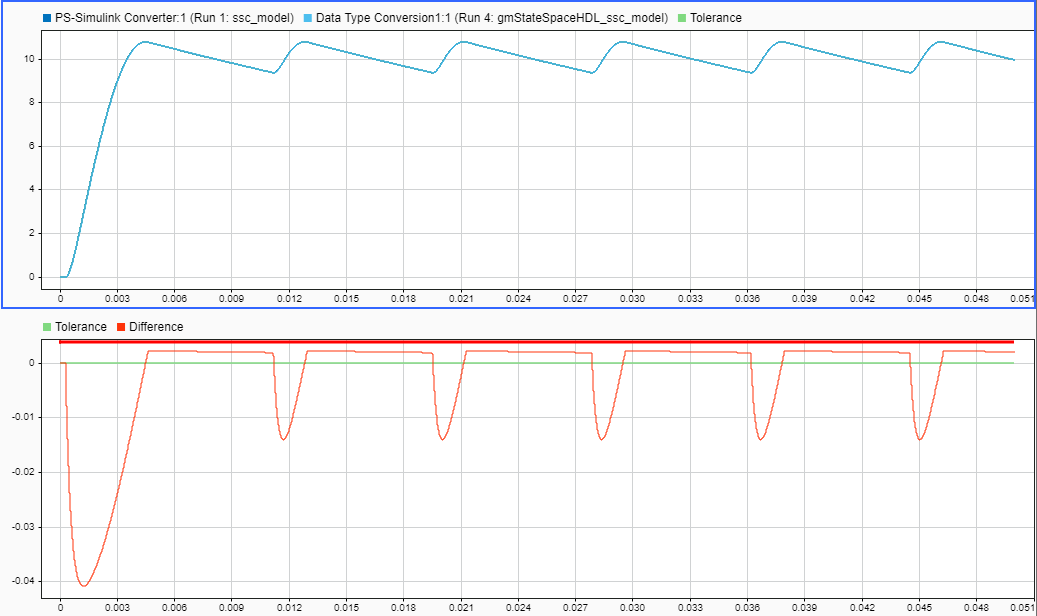

为了确保HDL子系统与原始Simscape模型相对应,模拟该模型并将结果与基线模拟结果进行比较。

%模拟sim卡(“gmStateSpaceHDL_ssc_model”)%获取模拟数据检查器运行idrunIDs = 万博1manbetxSimulink.sdi.getAllRunIDs;runBaseline = runid (end - 3); / /结束runHDLImplementation = runIDs(结束);%打开模拟数据检查器万博1manbetxsimulink .sd .view = simulink .sd . compareruns (runBaseline,...runHDLImplementation);

结果与基线结果相似。Simscape模型与HDL代码生成兼容。

从实现生成HDL代码:

从HDL实现模型访问配置参数窗口。扩大HDL代码生成并选择报告.在方框中勾选生成可跟踪性报告和生成资源利用率报告选项。

运行

hdlsetup函数。hdlsetup (“gmStateSpaceHDL_ssc_model”)保存模型和子系统参数设置。

hdlsaveparams (“gmStateSpaceHDL_ssc_model”);%% Set Model 'gmStateSpaceHDL_ssc_model' HDL parameters hdlset_param('gmStateSpaceHDL_ssc_model', 'FloatingPointTargetConfiguration', hdlcoder。createFloatingPointTargetConfig(“NativeFloatingPoint”……,‘延迟策略’,‘MIN’)……);hdlset_param('gmStateSpaceHDL_ssc_model', ' hdl子系统','gmStateSpaceHDL_ssc_model/HDL子系统');hdlset_param (' gmStateSpaceHDL_ssc_model ', ' MaskParameterAsGeneric ', '对');hdlset_param(“gmStateSpaceHDL_ssc_model”、“过采样”,49);%设置子系统的HDL参数hdlset_param('gmStateSpaceHDL_ssc_model/HDL子系统',' flatflathierarchy ', 'on');hdlset_param('gmStateSpaceHDL_ssc_model/HDL子系统/HDL算法/模式选择/生成模式向量','架构','MATLAB数据路径');%设置子系统HDL参数hdlset_param('gmStateSpaceHDL_ssc_model/HDL子系统/HDL算法/状态更新/乘状态','SharingFactor', 1);保存验证模型生成设置。

HDLmodelname =“gmStateSpaceHDL_ssc_model”;hdlset_param (HDLmodelname“GenerateValidationModel”,“上”);

生成HDL代码。

makehdl(“gmStateSpaceHDL_ssc_model / HDL子系统”)###为“gmStateSpaceHDL_ssc_model/HDL子系统”生成HDL。###使用模型gmStateSpaceHDL_ssc_model的配置集作为HDL代码生成参数。###运行HDL检查模型'gmStateSpaceHDL_ssc_model'###开始编译模型'gmStateSpaceHDL_ssc_model'…###在模型“gmStateSpaceHDL_ssc_model”上应用HDL优化……###您所选择的代码生成和优化选项引入了额外的管道延迟。###延迟平衡特性自动插入匹配延迟进行补偿### DUT需要一个初始管道设置延迟。每个输出端口都会经历这些额外的延迟。###输出端口1:1周期。 ### Begin model generation. ### Model generation complete. ### Clock-rate pipelining results can be diagnosed by running this script: hdlsrc\gmStateSpaceHDL_ssc_model\highlightClockRatePipelining.m ### To clear highlighting, click the following MATLAB script: hdlsrc\gmStateSpaceHDL_ssc_model\clearhighlighting.m ### Generating new validation model: gm_gmStateSpaceHDL_ssc_model_vnl. ### Validation model generation complete. ### Begin VHDL Code Generation for 'gmStateSpaceHDL_ssc_model'. ### MESSAGE: The design requires 49 times faster clock with respect to the base rate = 3.33333e-06. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem7 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem6 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem5 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block1.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem4 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block2.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem3 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block3.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem2 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block4.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/HDL Algorithm/Mode Selection/State Mode Vector To Index/Subsystem1 as ... hdlsrc\gmStateSpaceHDL_ssc_model\Subsystem1_block5.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_mul_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_mul_single.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_add_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_add_single.vhd. ### Working on dot_product_2 as hdlsrc\gmStateSpaceHDL_ssc_model\dot_product_2.vhd. ### Working on dot_product_1 as hdlsrc\gmStateSpaceHDL_ssc_model\dot_product_1.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_uminus_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_uminus_single.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem/nfp_relop_single as hdlsrc\gmStateSpaceHDL_ssc_model\nfp_relop_single.vhd. ### Working on HDL Subsystem_tc as hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_tc.vhd. ### Working on gmStateSpaceHDL_ssc_model/HDL Subsystem as hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem.vhd. ### Generating package file hdlsrc\gmStateSpaceHDL_ssc_model\HDL_Subsystem_pkg.vhd. ### Code Generation for 'gmStateSpaceHDL_ssc_model' completed. ### Creating HDL Code Generation Check Report HDL_Subsystem_report.html ### HDL check for 'gmStateSpaceHDL_ssc_model' complete with 0 errors, 7 warnings, and 2 messages. ### HDL code generation complete.

HDL代码生成报告将打开,并包含所有生成的错误或警告。该报告包含指向资源利用率报告的链接,该报告描述了FPGA部署的资源需求。

生成的HDL代码和验证模型保存在

hdlsrc \ gmStateSpaceHDL_ssc_model \ html目录中。生成的代码保存为HDL_Subsystem_tc.vhd.要生成用于部署到指定目标的HDL代码,请使用HDL Workflow Advisor。

另请参阅

块

Simscape块

功能

simscape.findNonlinearBlocks|hdladvisor(高密度脂蛋白编码器)|hdlsaveparams(高密度脂蛋白编码器)|hdlset_param(高密度脂蛋白编码器)|hdlsetup(高密度脂蛋白编码器)|makehdl(高密度脂蛋白编码器)|sschdladvisor(高密度脂蛋白编码器)

相关实例

- 查看样本时间信息

- 为Simscape模型生成HDL代码(高密度脂蛋白编码器)

- 为Simscape万博1manbetx两级转换器模型生成Simulink实时接口子系统(高密度脂蛋白编码器)

- Simscape直流电机控制到兼容hdl的Simulink模型的故障诊断转换万博1manbetx(高密度脂蛋白编码器)

- Simscape永磁同步电机到hdl兼容Simulink模型的故障诊断转换万博1manbetx(高密度脂蛋白编码器)

- 在仿真数据检查器中查看数据

更多关于

- 开始使用HDL工作流顾问(高密度脂蛋白编码器)

- 创建和使用代码生成报告(高密度脂蛋白编码器)

- 半实物仿真的工作流

- 实时模型准备工作流程

- 实时仿真的工作流