主要内容

部署

创建包含用户编程的比特流并将其下载到FPGA处理器芯片

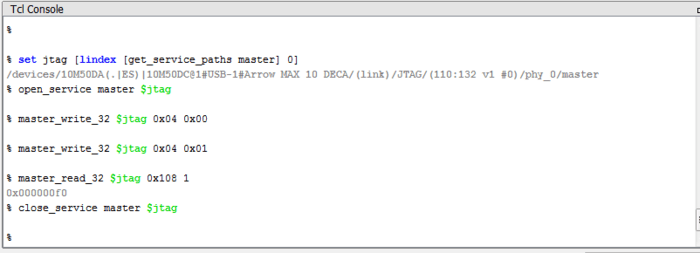

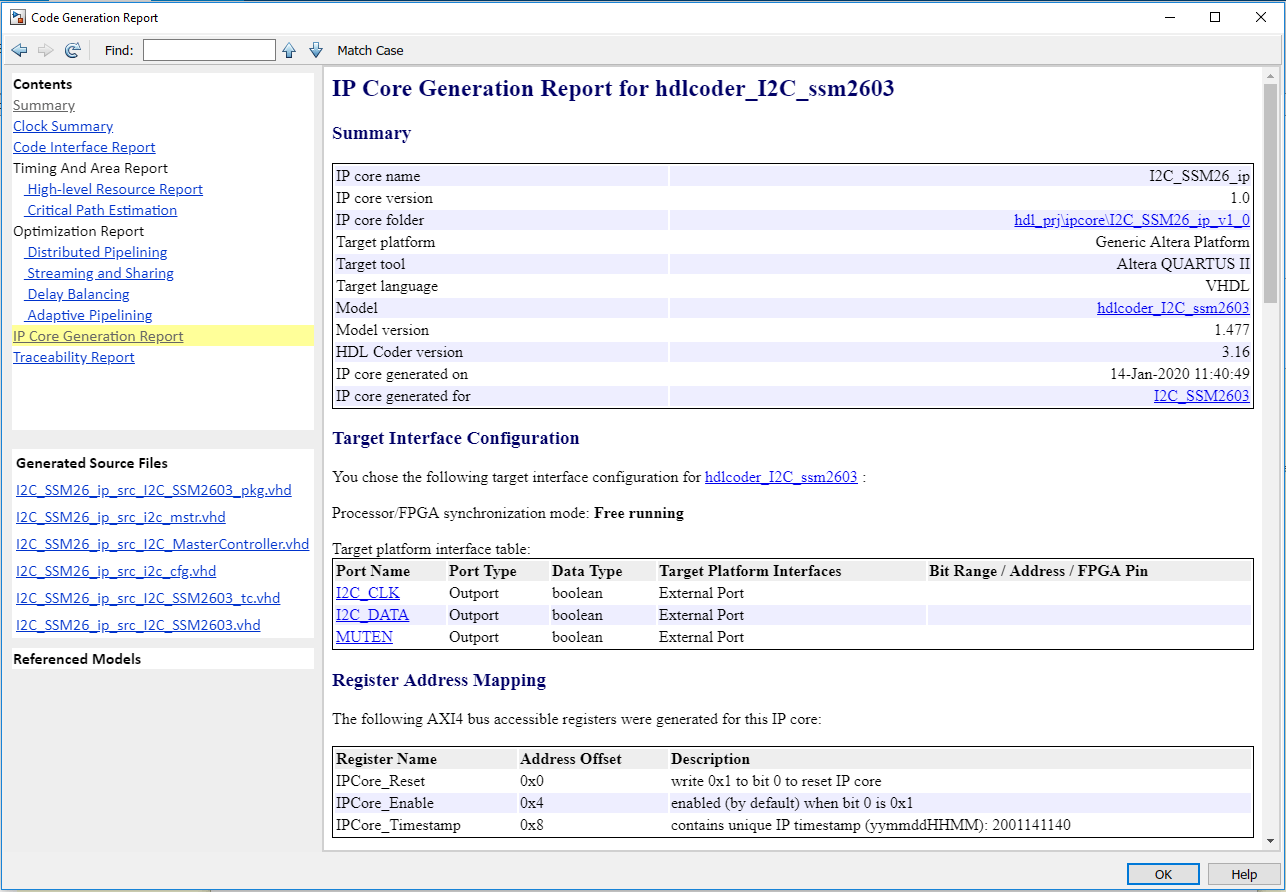

要对FPGA进行编程并在硬件上运行算法,HDL Coder™可以生成IP内核,并将其部署到英特尔®FPGA板。您还可以使用FPGA交钥匙工作流程编程FPGA板,该工作流为算法和FPGA顶级包装器生成HDL代码,然后将您的设计部署到电路板。

话题

FPGA交钥匙

FPGA交钥匙工作流程用于部署到独立FPGA硬件。

Simulink的独立Altera FPGA开发板万博1manbetx

此示例显示了如何定位Altera®FPGA开发板合成使用FPGA交钥匙工作流程。