使用Xilinx RFSoC设备发送和接收音调-第2部分部署

这个例子展示了如何使用SoC Blockset®在Xilinx®RFSoC设备上实现和验证设计。您将在Xilinx RFSoC评估套件上部署一个系统,该系统从FPGA生成正弦音调,通过多个射频通道传输它,并将它接收回设备,以完成环回。有关系统的建模和仿真,请参阅使用Xilinx RFSoC器件发送和接收音调-第1部分系统设计实例

万博1manbetx支持硬件平台:

Xilinx®Zynq UltraScale®+ ZCU111评估试剂盒+ XM500 Balun卡

Xilinx®Zynq UltraScale®+ZCU216评估套件+XM655巴伦卡

硬件实现和运行

硬件设置的ZCU111工具包

根据下表提供的连接方式,连接XM500 Balun卡上的SMA连接器,以完成dac和adc之间的环回。使用直流块差分通道环回。

实现该模型soc_rfsoc_datacapture在受支持的万博1manbetxSoC板上,使用SoC建设者工具。确保硬件板选项设置为Xilinx®Zynq UltraScale+(R) ZCU111检测试剂盒上片上系统Simulink to万博1manbetxolstrip的选项卡。

打开SoC建设者,单击配置、构建和部署按钮。SoC Builder工具打开后,按照以下步骤操作:

在“设置”屏幕上选择“构建模型”。单击“下一步”。

单击“查看/编辑内存映射”在“查看内存映射”屏幕上查看内存映射。单击“下一步”。

在“选择项目文件夹”屏幕上指定项目文件夹。单击“Next”。

在“选择构建动作”屏幕上选择“构建外部模式”。单击“Next”。

单击“验证”以在“验证模型”屏幕上检查要实施的模型的兼容性。单击“下一步”。

点击“构建”,在“构建模型”屏幕上开始构建模型。当FPGA合成开始时,一个外部外壳打开。单击“Next”。

单击“连接硬件”屏幕上的“测试连接”,测试主机与SoC板的连接。单击“下一步”转到“运行应用程序”屏幕。

FPGA综合可能需要30分钟以上的时间。为了节省时间,您可以按照以下步骤使用预先生成的位流。

关闭外壳以终止合成。

在MATLAB命令提示符下输入此命令,将预生成的位流复制到您的项目文件夹中。

点击“加载和运行”按钮加载预生成的比特流并在SoC板上运行模型。

copyfile(完整文件(matlabshared.supp万博1manbetxortpkg.getSupportPackageRoot,“工具箱”,“soc”,“万博1manbetxsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,'soc_rfsoc_datacapture-Xilinxzynkltrascale_RFSoCZCU111EvaluationKit.bit'),”。/ soc_prj ');

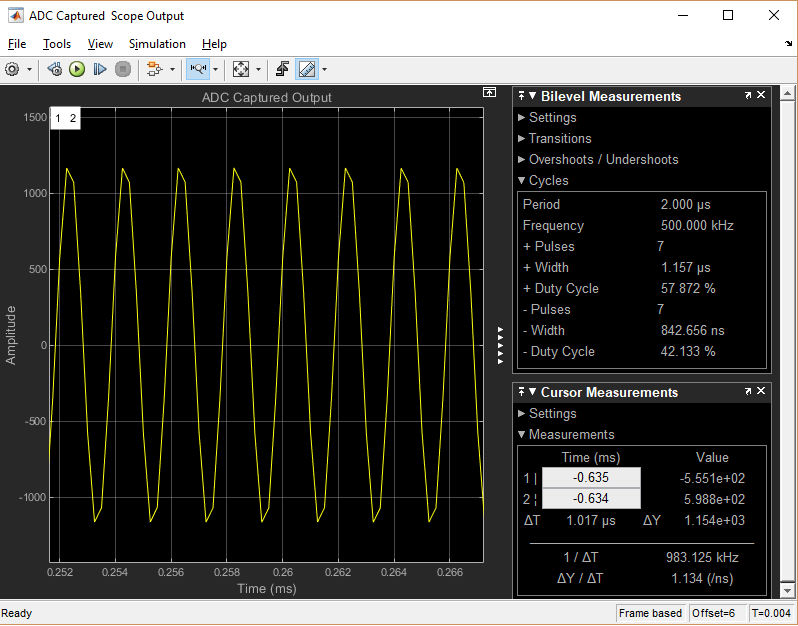

加载位文件后,打开生成的软件模型,从顶部模型复制频谱分析仪和示波器,并连接到速率转换块,如图所示,然后运行模型。您可以在频谱分析仪中观察ADC通道1默认的音调频率。

在外部模式下运行模型,并验证频谱分析仪上接收到的音调是否为0.5 MHz。默认情况下,ADC通道1配置为可视化。要选择其他ADC通道,请修改adcChannelSelect参数。通过各种DAC通道传输的音调信号按不同比例缩放。这被视为频谱范围内接收音调峰值的差异。例如,使用adcChannelSelect与通道1相比,参数值5(对应于通道5)导致频谱分析仪上的峰值较低。

请注意:在XM500 Balun卡的通道3和通道4中看不到任何输出。这些通道支持1到4 GHz范围,高于0.5 MHz的传输音调。万博1manbetx

在ZCU216硬件上实现并运行

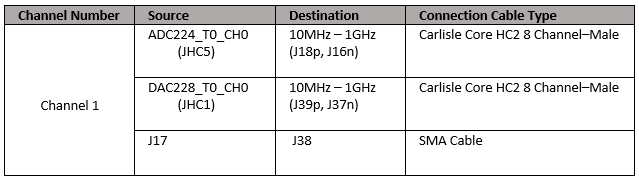

硬件设置:连接XM655 Balun卡,完成dac和adc之间的环回,如表所示。

实现该模型soc_rfsoc_IQ_datacapture_top在支持的S万博1manbetxoC板上,使用SoC Builder工具。确保硬件板选项设置为Xilinx®Zynq UltraScale+(R)ZCU216评估套件上片上系统,并遵循上一节中定义的万博1manbetx相同socBuilder步骤,但要加载预生成的位流,请对ZCU216评估工具包使用以下命令。

copyfile(完整文件(matlabshared.supp万博1manbetxortpkg.getSupportPackageRoot,“工具箱”,“soc”,“万博1manbetxsupportpackages”,“xilinxsoc”,“xilinxsocexamples”,“比特流”,“soc_rfsoc_IQ_datacapture_top-XilinxZynqUltraScale_RFSoCZCU216EvaluationKit.bit”),”。/ soc_prj ');

在外部模式下运行软件模型,在Spectrum Analyzer上验证接收到的音调为0.5 MHz。

分析结果

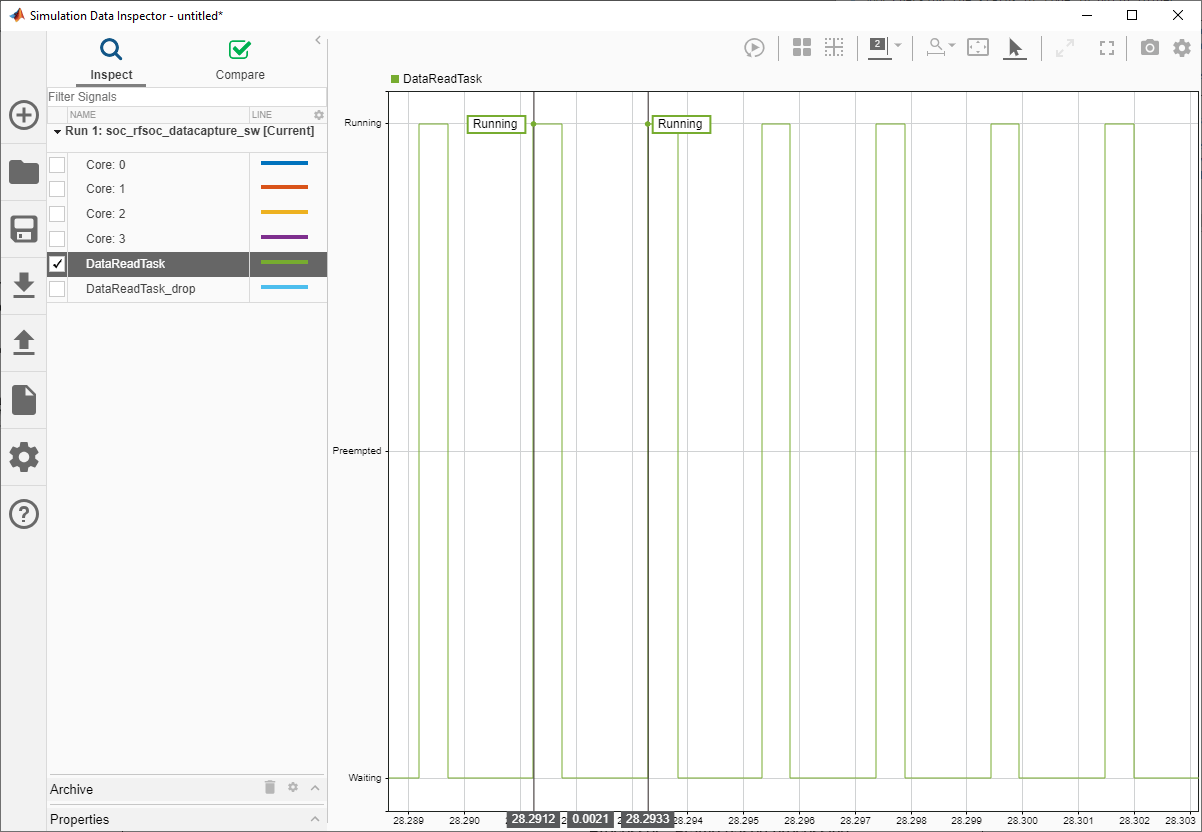

您可以使用SoC块集的设备上评测功能评测处理器任务持续时间的执行。此工具有助于调试和验证任务是否使用从FPGA异步接收的数据及时完成。

要启用处理器任务评测,请在生成的软件模型中打开配置参数对话框,然后选择硬件实现>硬件板设置>处理器上的任务分析选择节目SDI然后选择保存到文件.

集仪表代码。设置仿真停止时间为10秒,在外部模式下运行模型。仿真完成后,打开仿真数据检查器(SDI),导航到最近的运行,并添加一个信号DataReadTask的阴谋。从图中你可以观察到帧速率为2毫秒。

总结

这个例子演示了如何通过在Xilinx RFSoC设备上包含射频数据转换器来实现无线设计。使用SoC Builder,您实现了一个从FPGA生成音调的系统,并通过RF数据转换器块执行环回。您验证了系统在硬件上按预期工作。