AXI4-Stream IIO写

库:

嵌入式编码器为Xilinx Z万博1manbetxynq平台支持包

描述

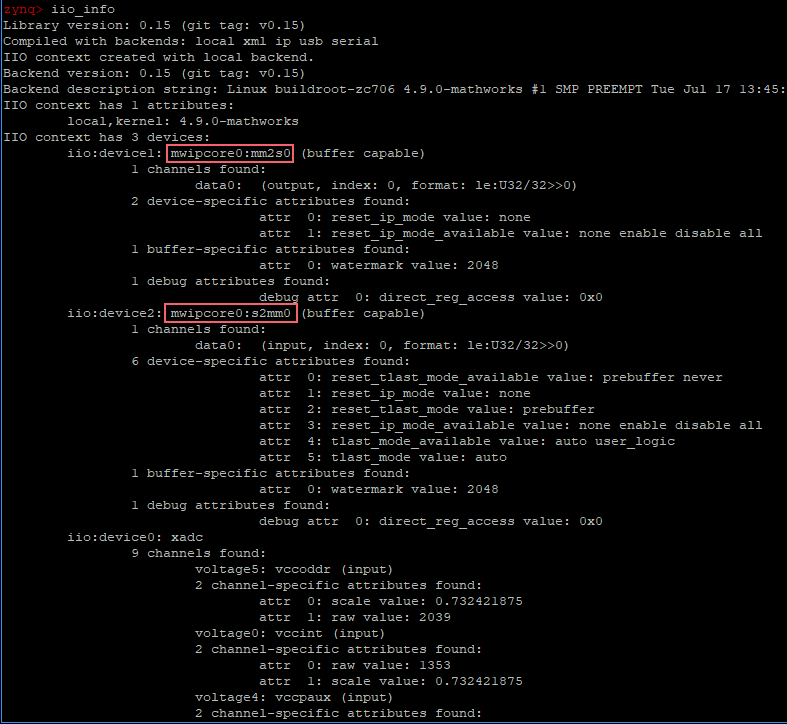

这写数据块直接内存访问(DMA)指定的缓冲区AXI4-Stream IP核心设备通过使用工业I / O (IIO)库的司机。的AXI4-Stream IIO写块使低延迟、高通量数据传输模型的处理器的IP核心FPGA。这个图表显示了控制信号和路径的数据离开这个街区后. .

港口

输入

输出

参数

提示

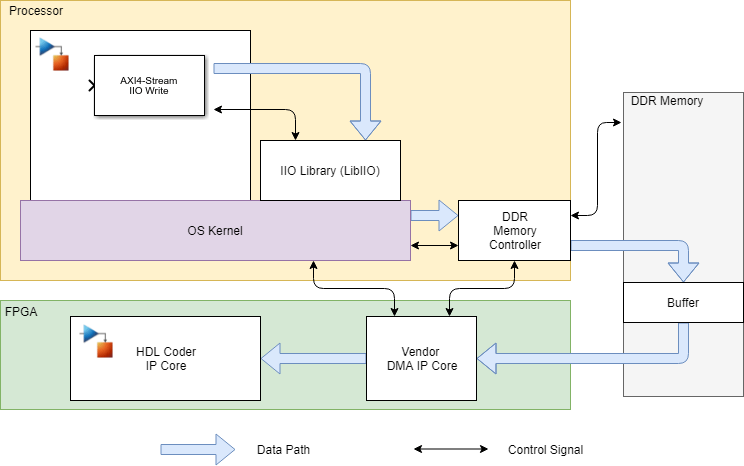

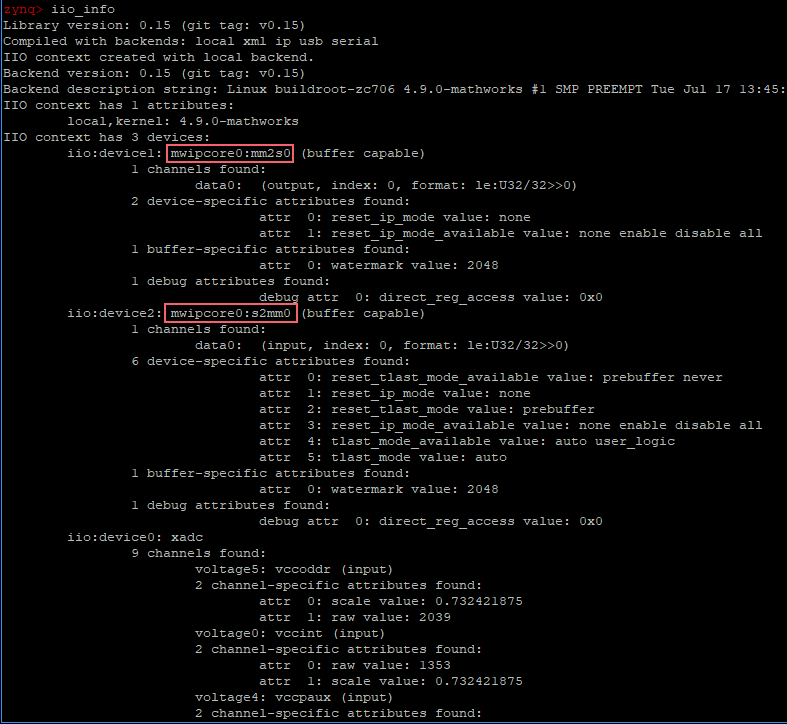

可用IIO设备名称的列表和渠道,在Xilinx打开终端®Zynq®硬件板,并执行该命令。

iio_info

版本历史

介绍了R2018b