信号完整性的工具箱

高速シリアルおよびパラレルリンクのシミュレーションおよび解析

信号完整性的工具箱™には,高速のシリアルリンクとパラレルリンクを設計するための関数とアプリが用意されています。複数のパラメーターで試行し,設計メトリクスを抽出し,波形と結果を可視化できます。送信機,受信機,チャネルの相互作用を解析することで,オペレーティングマージンとリンク性能を予測できます。

このツールボックスは,統計および時間領域シミュレーションを行うための規格に準拠したIBIS-AMIモデルをサポートしており,イコライゼーションとクロックリカバリを解析します。マルチポート年代パラメーターデータ,宜必思,HSPICE,解析モデルを使用してチャネルを記述できます。

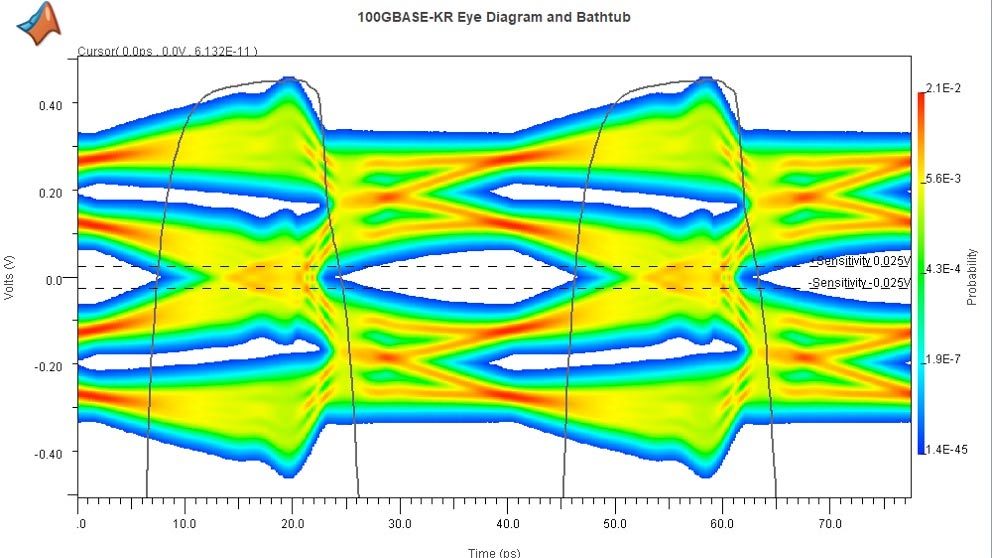

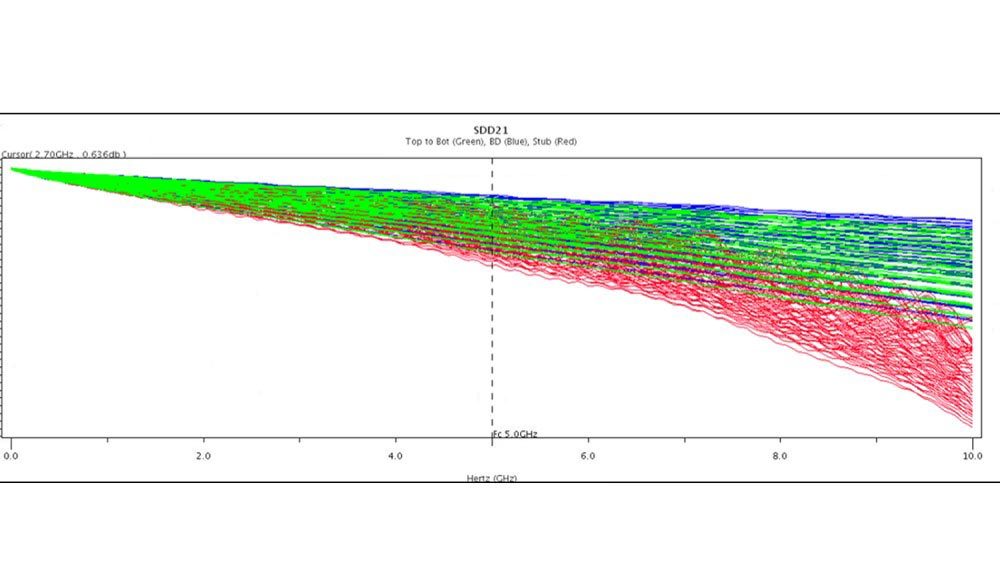

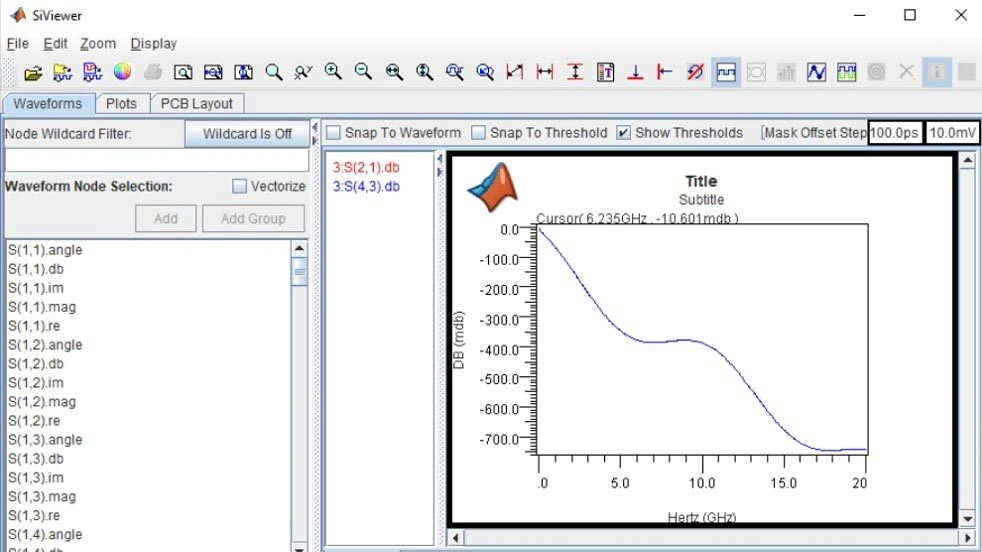

信号完整性的工具箱を使用すると,ISI,ジッター,ノイズなどの影響を観察しながら,波形とアイダイアグラムを解析し,チャネル品質を測定できます。周波数領域でチャネルの挿入損失,反射損失,クロストークを解析し,IEEE®802.3、OIF作为PCIe, DDRを含む業界標準への準拠を検証できます。

レイアウトの前に,トレードオフを評価し,コスト,パフォーマンス,信頼性,コンプライアンスに関してパラレルリンクとシリアルリンクを最適化できます。その後,システムのポストレイアウト検証を実行し,シミュレーションの結果を測定データと関連付けることができます。

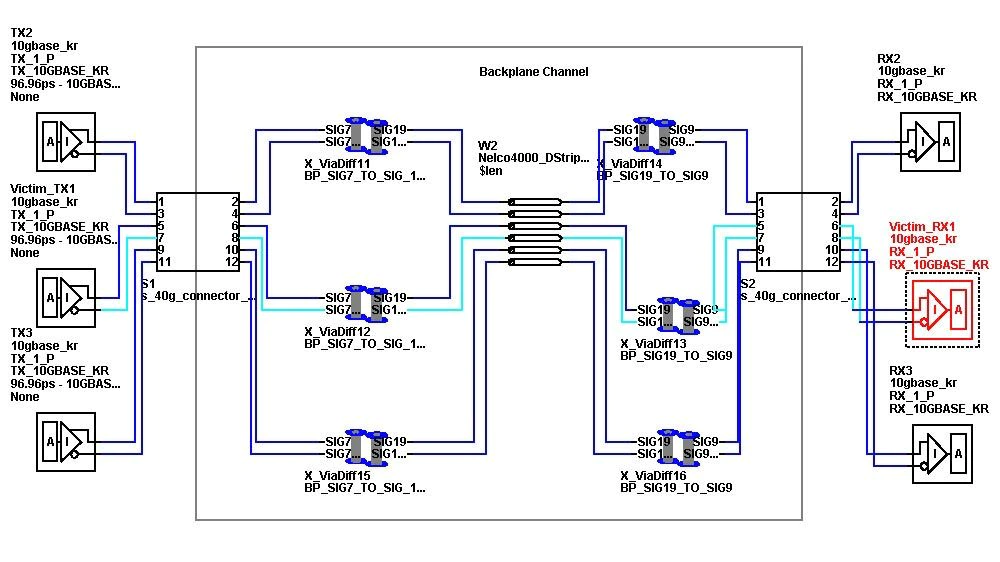

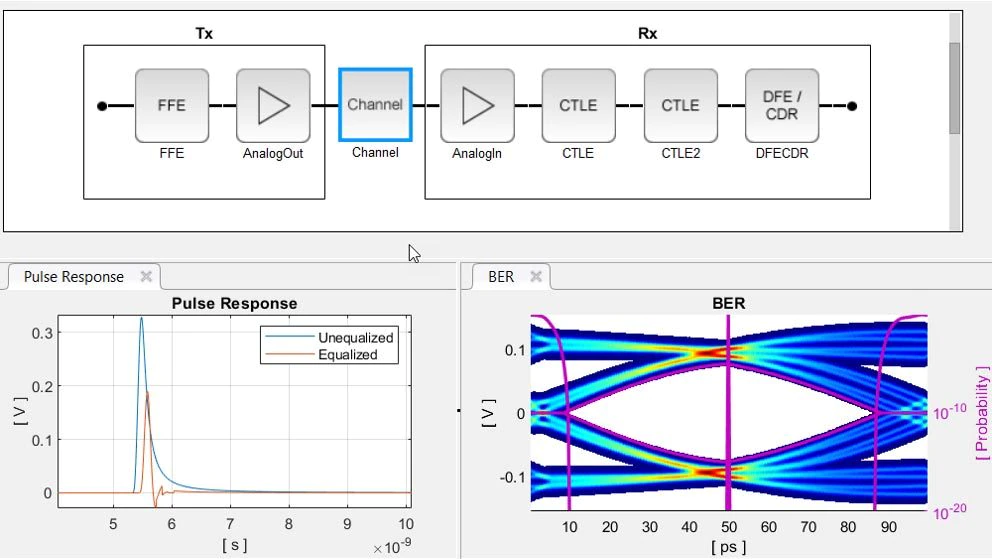

シリアルリンク解析

串行连接设计师アプリを使用すると,マルチギガビットシリアルリンクのエンドツーエンドのプリレイアウト解析を実行できます。IBIS-AMIモデル,PCBトレース,ビア,コネクタを使用すると,損失,反射,クロストークなどを解析できます。

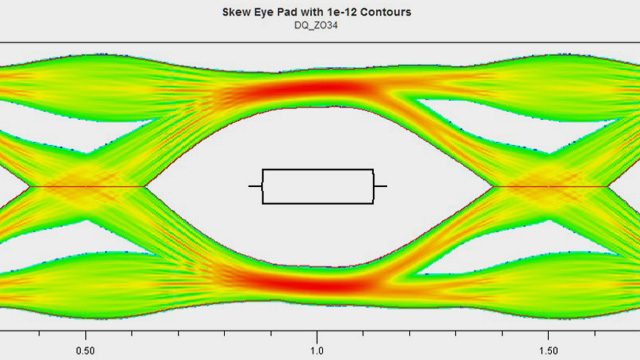

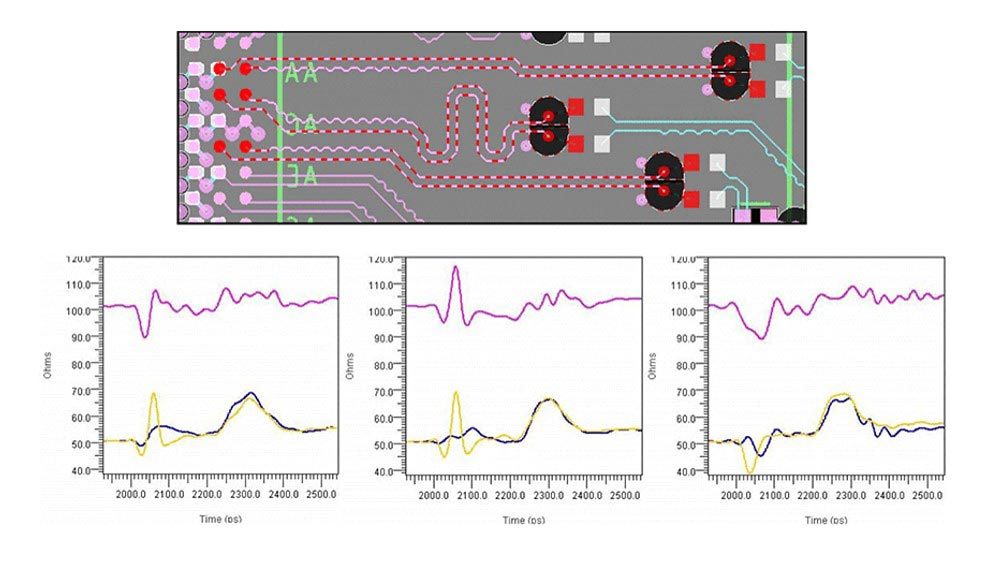

パラレルリンク解析

并行链接设计师アプリを使用すると,セットアップとホールドのタイミングに加え,高速パラレルリンクの電圧余裕を判断できます。パラレルインターフェイスを解析して,タイミングとシグナルインテグリティの制約条件への準拠を確認します。

規格への準拠

作为PCIe DDR, USB,イーサネット,その他の規格に利用可能な40以上のコンプライアンスキットのいずれかを使用して,シリアルリンクとパラレルリンクが業界標準に準拠しているかを確認します。