IntelSoC Devices

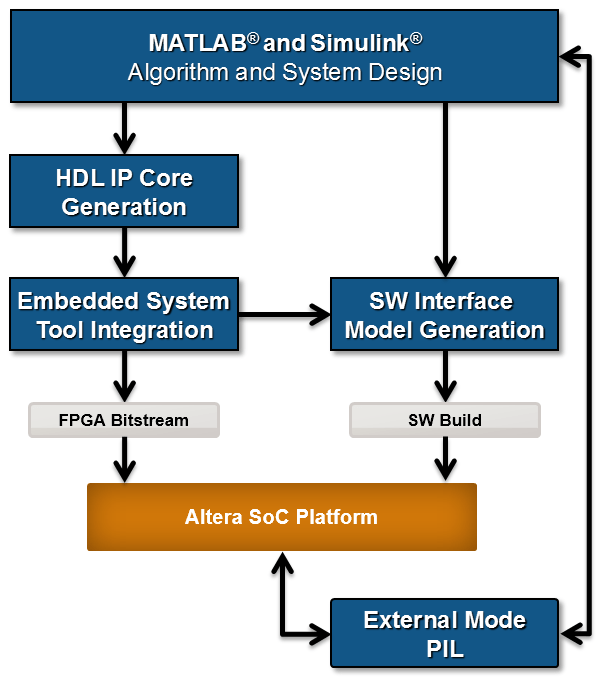

HDL Coder™可以生成IP核心,将其集成到您的QSYS项目中,并编程Intel硬件。使用嵌入式编码器®, you can generate and build the embedded software, and run it on the ARM®processor. SeeHardware-Software Co-Design Workflow for SoC Platforms。

To deploy your design to the Intel SoC device, you must install theHDL编码器支持包适万博1manbetx用于英特尔SOC设备。有关安装信息,请参阅HDL编码器支持硬件万博1manbetx。

Classes

Functions

Topics

- 模型设计AXI4奴隶接口的一代

How to design your model for AXI4 or AXI4-Lite interfaces for scalar, vector ports, bus data types, and read back values.

- AXI4流界面生成的型号设计

How to design your model for AXI4-Stream vector or scalar interface generation.

- AXI4主界面生成的型号设计

AXI4主协议的描述,以及如何使用Axi4-Master接口为IP核心生成设计模型。

- Program Target FPGA Boards or SoC Devices

How to program the target Intel or Xilinx Hardware.

Related Information

Troubleshooting

Resolve Timing Failures in IP Core Generation and Simulink Real-Time FPGA I/O Workflows

Resolve timing failures in Build FPGA Bitstream step of IP Core Generation Workflow or Simulink Real-Time FPGA I/O Workflow for Vivado-Based Boards.