从行为模型设计法ADC Verilog硬件描述语言(VHDL)

通过阿里Behboodian MathWorks MathWorks和杰夫·米勒

使用不同的工具和语言开发模拟混合信号集成电路设计过程中容易出错,耗时、复杂。基于模型的设计解决这些问题通过允许工程师完成所有设计阶段MATLAB和万博1manbetx。通过使用仿真软件模型设万博1manbetx计的基石,团队可以验证设计在开发的所有阶段,减少昂贵的结构性变化或发现错误的机会在实现阶段。

在本文中,我们使用基于模型的设计与MATLAB仿真软件设计法模拟-数字转换器(ADC)。万博1manbetx从ADC的高级行为模型开始,我们精心设计和最后,生成synthesizable硬件描述语言(VHDL)的代码。

这个设计是可用的文件下载。我们鼓励您打开仿真软件模型,探索设计的不同方面。万博1manbetx

法ADC转换器

法ADC转换器几乎只在应用程序需要使用高分辨率输出,如高保真音频或工业测量。为了实现所需的高分辨率,必须将模拟信号采样速率远高于奈奎斯特速率。一般来说,电路设计的复杂性采样率成正比。出于这个原因,法adc历来用于抽样低频信号,信号与奈奎斯特率相对较低,如演讲手机。

法ADC包括模拟和数字部分(图1)。模拟部分,包括一个迴路,样本的输入在一个较高的率和生成一个二进制输出的平均值随时间追踪模拟输入。数字部分,其中包括大量毁灭过滤,发现平均价值通过运行迴路的输出通过一个低通的冷杉过滤器。在本文稍后,我们将利用基于二进制的滤波器的输入来实现一个非常有效的滤波器结构。

开发一个行为模型

我们开始通过开发一个高级行为仿真软件模型。万博1manbetx浮点数的模型。我们用它作为系统的图形表示和一个可执行的规范。

滤波器在数字部分,MATLAB设计,是基于规格AD1877 16位法ADC模拟设备。单程冷杉滤波器,信号会毁坏了64倍,并且有大约3000水龙头。我们使用以下MATLAB脚本生成数字滤波器:

Decimation_Factor = 64;Passband_Ripple = .006;% dBStopband_Attenuation = 90;% dBFs = 48 e3;通频带= 21.6 e3;% dB阻带= 26.4 e3;% dBInput_Sampling_Rate = Decimation_Factor * Fs;f = fdesign.decimator (Decimation_Factor低通滤波器的、通带、阻带…Passband_Ripple、Stopband_Attenuation Input_Sampling_Rate);h =设计(f);

阐述设计

在这个阶段,行为模型尚未适合定点FPGA和ASIC实现。原因是,过滤器非常大,需要大量的计算。我们精心设计,我们将减少过滤器尺寸准备实施。我们将使用二进制输入滤波器的性质,使设计更有效。最后,我们将数字转换为定点。高级行为模型将作为一个参考。

优化滤波器设计

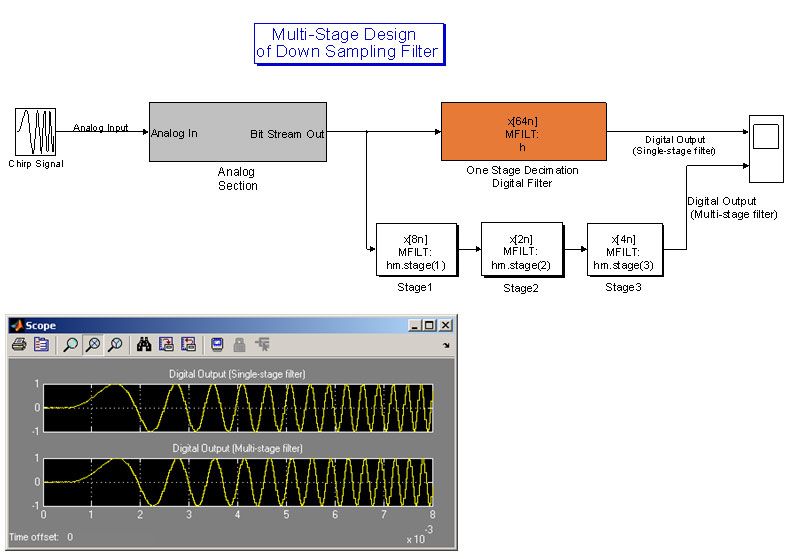

单程过滤约有3000水龙头,我们最初的数字滤波器需要大量的算术运算符。使用MATLAB,我们把它分成三阶段大量毁灭过滤器(图2),每个阶段都有40,12日和194年过滤器阀门,分别和每个阶段会毁坏信号8倍,2和4,分别为64。这种方法可以降低系数的总数大约10倍,明显减少算术运算所需的数量。

我们比较原始单程滤波器的频率响应与新三级过滤器(图3)。我们看到的幅度响应三级过滤匹配原始单程滤波器的幅度响应非常密切。

在仿真软件环境万博1manbetx中,我们阐述了设计和测试验证它与行为模型比较好(图4)。使用多速率,多级滤波器的设计大大降低了计算复杂度,但引入了一个更大的群延迟滤波器。这个大延迟是明显的在滤波器输出的痕迹显示在图4中,在第二年底痕迹明显落后于第一跟踪结束,因为大过滤器的延迟。

阐述在第一阶段的过滤器

如前所述,第一阶段是40-tap冷杉过滤器。一般来说,实现这样一个筛选我们需要40次乘法和39增加对每一个输出示例。然而,随着模拟部分提要一个二进制信号滤波器的第一阶段,我们可以使用查找表实现第一阶段。这种方法不需要乘法,只有4添加。其他两个阶段将以传统的方式执行。

理解我们如何取代40-tap冷杉大批杀害8过滤器用查找表,首先让我们看看简单的案例8 8-tap冷杉大量毁灭的过滤器。在这种情况下,每8个二进制输入样本,过滤器生成一个输出示例。示例的输出取决于8输入样本和256年可以取不同值(因为每个样品只有两个级别)。查表将使用8个二进制输入样本作为一个索引来查找表256预先计算的过滤器输出。这将导致一个非常有效的过滤设计没有乘数。

使用这种方法,我们将40-tap滤波器分解成5段8水龙头。每一部分我们生成一个查表结合5查表输出产生整体的结果。你可以下载MATLAB代码我们使用生成的查找表条目。

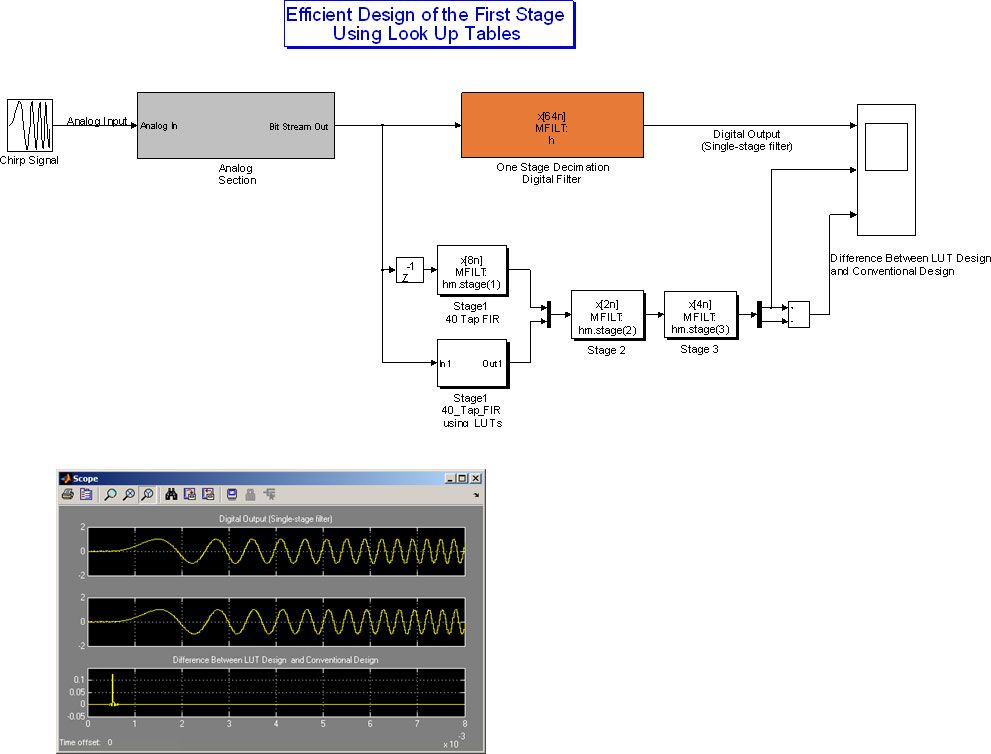

图5显示了最终的设计。设计是一个二进制信号的输入1或1。注意到设计使用一个将采样块和嵌入式MATLAB功能块。将采样块的输出比输入速度慢8倍。不同的颜色在图5中显示的信号有不同的利率。

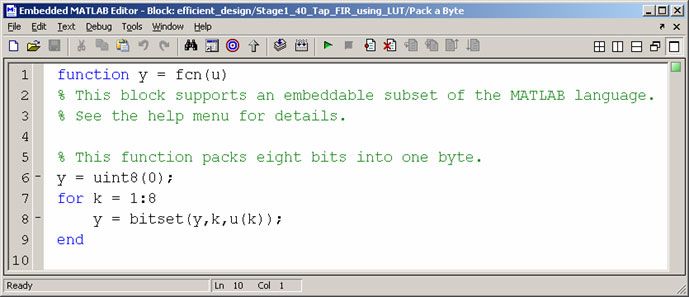

与嵌入的MATLAB函数我们可以把MATLAB代码块到仿真软件,然后模拟设计。万博1manbetx嵌入式MATLAB可以简化建模算法是最好的和最容易使用基于文本的建模。在这种情况下,MATLAB代码非常简单(图6)。

在这一点上我们确认设计功能正常。现在最好是识别出任何差异,而不是在随后的滤波器的硬件实现。仿真软件万博1manbetx模型如图7所示比较原始的输出滤波器与我们阐述了过滤器。我们最初看到的输出两个设计的差异,但这种差异随着时间的推移趋于零。不匹配的原因之间的区别是初始条件的原始设计,阐述了设计使用附近地区创建。我们可以通过设置适当的初始条件和消除不匹配将额外的延迟块。

将模型转换为定点

到目前为止,我们所有的模型使用浮点算术。对于高效的FPGA和ASIC实现,我们必须将我们的模型转换为定点(图8)。我们用MATLAB和Simulink转换过滤器不动点。万博1manbetx在仿真软件环境万博1manbetx中,每个运算块可以处理浮点和定点计算,简化了转换过程。我们使用仿真软万博1manbetx件验证定点设计的输出匹配的参考设计。

高密度脂蛋白代码生成

MathWorks工具使我们能够生成synthesizable硬件描述语言(VHDL)定点或Verilog代码,多重速率的系统,包括过滤器,嵌入式MATLAB功能块和其他块用于ADC的数字部分的设计。我们使用万博1manbetx仿真软件HDL编码器生成VHDL代码的第一阶段过滤器如图8所示滤波器设计高密度脂蛋白编码器生成VHDL代码从第二和第三阶段。图9显示部分的硬件描述语言(VHDL)生成代码,我们从第一阶段的过滤器。

万博1manbetx仿真软件HDL编码让我们生成的硬件描述语言(VHDL)或Verilog代码不同的硬件实现特定的块,如和,产品,和极大极小块。这些不同的实现通常速度和芯片面积之间的妥协。在我们的示例中,我们使用一个可选的控制文件探索替代的实现和块如图8所示,使用级联,后来树实现。

除了硬件描述语言(VHDL)或Verilog代码,仿真软件HDL编码器可以生成一个万博1manbetxcycle-accurate模型,对应于特定的实现选择了块的数目。图10显示了模型生成一个级联实现。图11显示了模型生成的树实现。我们可以模拟生成的模型并验证其对参考模型的输出。

合成的结果

硬件描述语言(VHDL)代码生成后,我们必须准备硬件实现的代码。为此我们合成的硬件描述语言(VHDL)代码生成的第一阶段的过滤和执行地点和路线Virtex - 4 vsx25-10 FPGA使用Xilinx ISE软件工具。时机分析表明,我们可以运行设计的时钟频率210 MHz。

总结

在本文中,我们使用基于模型的设计和MathWorks工具创建一个高层,可执行法ADC的行为模型。我们阐述了行为模型准备在一个FPGA硬件实现。我们不断地在整个过程中验证了我们的模型的输出。这种方法使我们能够揭示设计的差异,如果离开了未被发现,可能会造成性能问题。我们使用仿真软件万博1manbetxHDL编码器生成HDL代码从模型并结合MATLAB代码到仿真软件模型中使用嵌入式MATLAB函数块。使用MATLAB和Simulink创建一个可执行的模型是这个设计的基础方法。万博1manbetx

2007年出版的