开始使用Simulink HDL协万博1manbetx同仿真

此示例指导您完成设置HDL验证器的基本步骤™ 在Simulink®环境中使用协同模拟向导的应用程序。万博1manbetx

协同仿真向导是一个图形用户界面(GUI),它指导您完成在MATLAB®或Simulink®和硬件描述语言(HDL)模拟器之间建立协同仿真的过程。万博1manbetx

在本例中,使用Simulink和ModelSim®万博1manbetx验证用Verilog编写的升余弦滤波器的设计。升余弦滤波器是数字通信系统中常用的脉冲整形滤波器。它不会对调制脉冲的输入产生符号间干扰(ISI)。

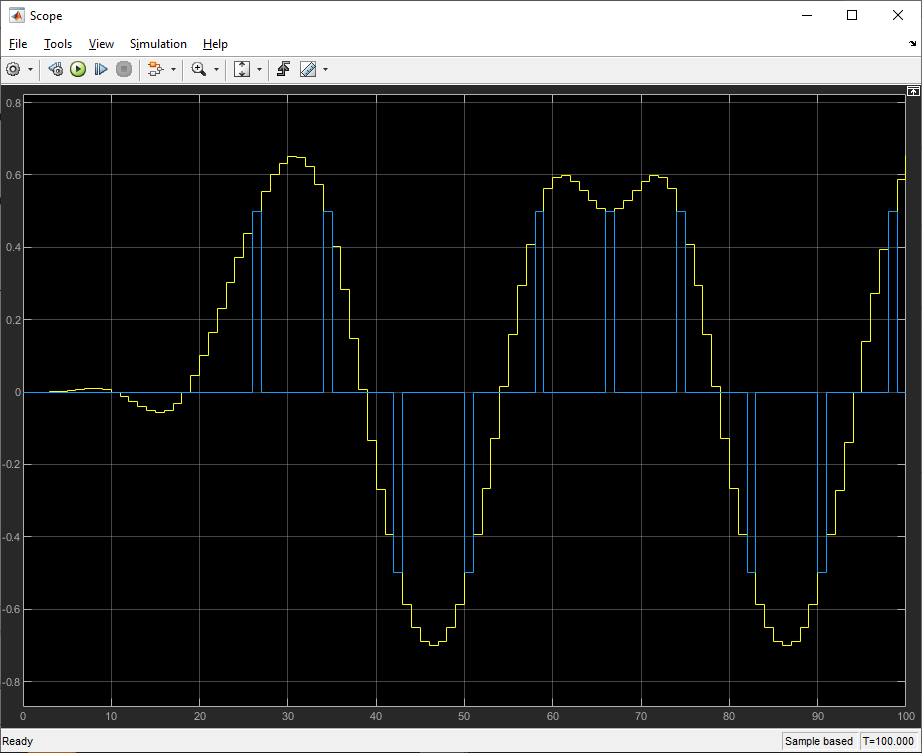

为了验证此升余弦滤波器的功能,提供了Simulink测试台。该测试台生成被测HDL设计(DUT)的输入,并绘制输入和输出万博1manbetx波形。

Cosimulation Wizard将此升高的余弦滤波器的Verilog文件作为其输入。它还收集在每个步骤中设置协同模拟所需的用户输入。在示例的最后,协同仿真向导生成一个Simulink模块,该模块表示Simulink模型中的HDL设计,一个编译HDL设计的MA万博1manbetxTLAB脚本,以及启动用于协同仿真的HDL模拟器的MATLAB脚本。在仿真过程中,可以在Simulink中看到该HDL滤波器的输入和输出波形。万博1manbetx

要求和先决条件

本例中需要这s manbetx 845些产品。

其中一个支持的HDL模拟器万博1manbetx:Mentor Graphics®ModelSim®/QuestaSim®或Cadence®Incisive®/Xcelium®

启动协同模拟向导

要从模型启动协同仿真向导,请选择应用程序选项卡,然后单击万博1manbetxHDL验证器.此操作将添加HDL验证器选项卡添加到Simul万博1manbetxink Toolstrip。然后,在模式节选择高密度脂蛋白Cosimulation.点击导入HDL文件在生成Cosim块部分。

使用协同模拟向导配置HDL协同模拟块

在Cosimulation类型页面,执行以下步骤:

如果您使用ModelSim或Questa,请离开高密度脂蛋白模拟器选择作为

ModelSim.如果你正在使用Incisive或Xcelium,请改变高密度脂蛋白模拟器选项厌恶的.保留默认选项在系统路径上使用HDL模拟器可执行文件选项,如果HDL模拟器可执行文件显示在系统路径上。如果路径上没有显示这些可执行文件,请单击浏览按钮以指定这些可执行文件的位置。

点击下一个转到HDL文件页面。

在高密度脂蛋白的文件页面,执行以下步骤:

点击添加然后选择其中一个

rcostflt_rtl.vVerilog或rcosflt_rtl.vhd硬件描述语言(VHDL)。查看文件列表中的文件,文件类型标识为您期望的类型。

点击下一个转到HDL编译页面。

在高密度脂蛋白编译页面中,协同仿真向导会在“编译命令”窗口中列出默认命令。在本教程中,您不需要更改这些命令。

当您使用自己的代码运行Cosimulation Wizard时,您可以在此窗口中添加或更改编译命令。

点击下一个继续到HDL模块窗格。这将反过来触发编译。MATLAB控制台显示编译日志。如果在编译期间发生错误,则该错误将出现在“状态”区域。

在模拟选项窗格,执行以下步骤:

指定用于协同模拟的HDL模块/实体的名称。从下拉列表中,选择

rcosflt_rtl. 此模块是用于联合仿真的Verilog/VHDL模块。如果你没有看到rcosflt_rtl在下拉列表中,可以手动输入文件名。对于连接方法选择

共享内存如果您的防火墙策略不允许TCP/IP套接字通信。

点击下一个转到Simulink端口窗格。协同模万博1manbetx拟向导使用指定的HDL模块和模拟选项在后台控制台中启动HDL模拟器。向导启动HDL模拟器后,向导将填充Verilog/VHDL模块上的输入和输出端口rcosflt_rtl并在下一步中显示它们。

在指定端口类型步骤,协同仿真向导将显示包含的输入和输出端口的两个表rcostflt_rtl分别地

协同仿真向导尝试识别每个端口的端口类型。如果向导错误地标识了端口,您可以使用这些表更改端口类型。

对于输入端口,您可以从

时钟,重置,输入或未使用.HDL验证器只连接标记的输入端口输入在联合万博1manbetx模拟期间进行模拟。HDL验证器连接有标记的输出端口

输出使用Sim万博1manbetxulink进行联合仿真。向导和Simulink忽略这些万博1manbetx标记的输出端口未使用在cosimulation。您可以更改标识为的信号的参数

时钟和重置在后面的步骤中。

接受默认端口类型并单击下一个转到输出端口详细信息页面。

在输出端口的详细信息页面,执行以下步骤:

设置的采样时间

filter_out到-1通过反向传播继承。您可以从Verilog代码中看到,Cosimulation Wizard表示

sfix34_En29格式。更改以下字段:

数据类型

定点签署

签署部分长度

29

点击下一个进入时钟/重置详细信息页面。

对于本例,请设置时钟周期(纳秒)为20。从Verilog代码中,可以知道重置是同步的,活动值是1。您可以在时间1纳秒时重置整个HDL设计,由时钟上升沿触发。复位信号的持续时间为15纳秒。

在时钟/复位页面,执行以下步骤:

设置HDL时间单位为

ns.设置时钟周期为20。

将活动边保留或设置为

上升.保留或设置重置初始值为1。

将复位信号持续时间设置为15。

点击下一个继续进入“开始时间对齐”页面。

开始时间校准页面显示时钟和复位信号波形图。Cosimulation向导用红线显示HDL开始Cosimulation的时间。开始时间也是Simulink从HDL模拟器获取第一个输入样本的时间。万博1manbetx

在开始时间对齐页,设置对齐方式。我们时钟的活动边是上升边。因此,在HDL模拟器的时间20ns时,提高的余弦滤波器的注册输出是稳定的。不存在竞争条件,默认的HDL启动协同仿真的时间(20 ns)是我们想要的模拟。您不需要对开始时间做任何更改。

点击下一个进行区块生成。

在生成HDL协同模拟块之前,您可以选择在完成协同模拟向导之前确定时间刻度。或者,您可以指示HDL验证器稍后计算时间刻度。连接生成的HDL协同模拟块的所有输入/输出端口并开始模拟后,验证软件将进行时间刻度计算。

在块生成页面,离开在模拟开始时自动确定时间刻度选择(默认)。稍后,您将有机会查看计算的时间尺度,并在进行模拟之前更改该值。

点击完成以完成协同模拟向导会话。

创建测试台以验证HDL设计

在本例中,是Simulink测试台模型万博1manbetxrcosflt_tb已经提供。你点击后完成在联合仿真向导中,Simulink在模型画布的中心插入以万博1manbetx下项目:

HDL协同模拟块

重新编译HDL设计的代码块(包含一个指向脚本的链接,通过双击该代码块启动)

启动HDL模拟器的块(包含一个指向脚本的链接,通过双击该块启动)

定位HDL协同仿真块,使常数和转换块排列成HDL协同仿真块的输入,总线排列成输出。连接块。您的模型现在看起来与下图类似。

协同仿真并验证HDL设计

双击标记为的块启动HDL模拟器发射HDL模拟器.

当HDL模拟器准备好后,返回到Simulink并开始模拟。万博1manbetx

确定时间表。回想一下在模拟开始时自动确定时间刻度“协同模拟向导”最后一页上的选项。执行此操作时,HDL验证器将启动“时间刻度详细信息”图形界面,而不是启动模拟。HDL模拟器和Simulink都对万博1manbetx

滤入和filter_out端口1秒。然而,它们在HDL模拟器中的采样时间应该与时钟周期(20纳秒)相同。改变Simulink的万博1manbetx采样时间/rcosflt\U rtl/clk到1(秒),然后按进来.向导然后更新表。下图显示了新的时间尺度:Simulink中的1秒对应于HDL模拟器中的2e-008秒。万博1manbetx

点击好吧关闭时间刻度详细信息对话框。重新启动Simu万博1manbetxlink仿真,从试验台模型的范围验证结果。

该范围显示延迟版本的输入提高余弦滤波器和该滤波器的输出。如果您直接对该过滤器的输出进行采样,则不会发生符号间干扰。