验证PID控制器的HDL实现使用FPGA-在半实物

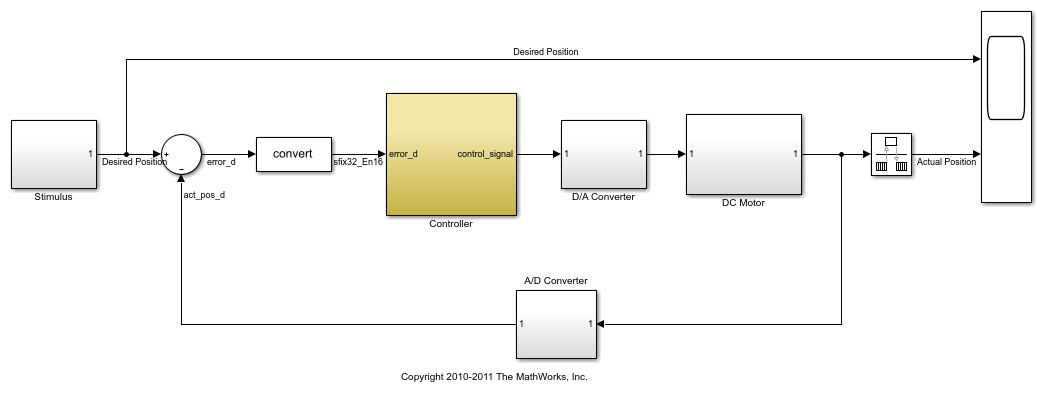

这个示例向您展示了如何使用HDL Verifier™设置循环中的fpga (FIL)应用程序。该应用程序使用Simulink®和FPGA万博1manbetx开发板来验证比例积分导数(PID)控制器的HDL实现。在本例中,Simulink生成电机万博1manbetx的期望位置,并模拟由PID控制器控制的电机。

要求和先决条件

s manbetx 845在这个例子中所需的产品:

MATLAB

万博1manbetx

定点设计师

HDL验证

FPGA设计软件(赛灵思ISE®设计套件,或赛灵思Vivado®设计套件,或英特尔Quartus®II设计软件,或Microsemi®Libero®SoC设计软件)

其中一个万博1manbetx支持FPGA开发板及配件

用于连接使用以太网:主机计算机上安装千兆位以太网适配器,千兆以太网跨接电缆

对于使用JTAG接口:USB声霸卡I或II线和驱动程序英特尔FPGA开发板。Digilent®JTAG电缆和驱动为Xilinx FPGA板。

对于使用的PCI Express连接:FPGA板安装到主机计算机的PCI Express插槽。

先决条件:

MATLAB®和FPGA设计软件可以安装在本地计算机或网络访问设备上。如果你使用的软件从网络上,您将需要在计算机中安装第二个网络适配器提供专用网络到FPGA开发板。请查看硬件和网络指南为您的计算机,以了解如何安装网络适配器。

第1步:设置FPGA开发板

如果您正在使用PCI Express连接进行模拟,请跳过此步骤和步骤2。如果你还没有建立你的一种总线标准快车连接,使用支持包安装软件引导你通过一种总线标准快车安装。万博1manbetx

使用以下步骤设置你的FPGA开发板。

确保电源开关还在从。

交流电源线连接到电源插头。将电源适配器线缆插入FPGA开发板。

直接连接以太网连接器上的FPGA开发板以太网适配器使用交叉以太网电缆将计算机上。

使用JTAG下载电缆将FPGA开发板与计算机连接。

确保在FPGA开发板所有跳线都在出厂默认位置。

第2步:设置主机电脑板连接

如果您使用JTAG连接进行模拟,请跳过此步骤。对于与以太网的连接,您的计算机上必须有一个千兆以太网网络适配器才能运行此示例。

在Windows®7,做以下步骤:

打开控制面板。

类型查看网络连接在搜索栏。选择查看网络连接在搜索结果中。

右击FPGA开发板的连接图标并选择属性从弹出菜单中。

下此连接使用下列项目, 选择Internet协议版本4 (TCP/IPv4)并点击属性。

选择使用下面的IP地址:。集IP地址192.168.0.1。如果您网络上的另一台计算机正在使用此地址,请将其更改为此子网上的任何可用IP地址,如192.168.0.100。这是你的主机地址。设置子网掩码255.255.255.0。您的TCP/IP属性现在看起来应该如下图所示:

在Windows®Vista中,请执行下列操作步骤:

打开控制面板。

请点击网络和共享中心,然后点击管理网络连接。

右击FPGA开发板的连接图标并选择属性从弹出菜单中。

下此连接使用下列项目, 选择Internet协议版本4 (TCP/IPv4)并点击属性。

选择使用下面的IP地址:。集IP地址至192.168.0.1。如果您网络上的另一台计算机正在使用此地址,请将其更改为此子网上的任何可用IP地址,如192.168.0.100。这是你的主机地址。设置子网掩码255.255.255.0。

在WindowsXP®,请执行下列操作步骤:

打开控制面板。

打开网络连接。

右击FPGA开发板的连接图标并选择属性从弹出菜单中。

下此连接使用下列项目, 选择互联网协议(TCP / IP)并点击属性。

选择使用下面的IP地址:。集IP地址192.168.0.1。如果您网络上的另一台计算机正在使用此地址,请将其更改为此子网上的任何可用IP地址,如192.168.0.100。这是你的主机地址。子网掩码设置为255.255.255.0。

在Linux®:

使用使用ifconfig命令来设置您的本地地址。例如:

%的ifconfig eth1的192.168.0.1

在本例中,eth1是Linux计算机上的第二个以太网适配器。检查您的系统,以确定哪个以太网适配器连接到FPGA开发板。上面的命令将本地IP地址设置为192.168.0.1。如果该地址是通过使用网络上的另一台计算机,将其更改为该网段上的任何可用的IP地址,如192.168.0.100。

步骤3:准备示例资源

建立一个例子文件夹,复制文件,例如,建立访问FPGA设计软件和开放模式。

1.您的MATLAB安装文件夹的,可以在其中复制示例文件范围之外创建一个文件夹。该文件夹必须是可写的。这个例子假设该文件夹位于在C:\ MyTests。

2.启动MATLAB和MATLAB将当前目录到您刚才创建的文件夹。例如:

光盘C:\ MyTests

3.输入以下MATLAB命令:

copyFILDemoFiles('的pid')

此命令创建子文件夹\ pid_hdlsrc将所有源文件复制到当前文件夹中matlabroot \工具箱\共享\ EDA \ FIL \ fildemos \ fil_pid进去。matlabroot是系统上的MATLAB根文件夹。现在,您将有以下文件C:\ MyTests \ pid_hdlsrc:

D_component.vhd

I_component.vhd

Controller.vhd

4.建立FPGA设计软件

利用FPGA-在环仿真之前,访问FPGA设计软件设置您的系统环境。您可以使用该功能hdlsetuptoolpath将ISE、Vivado、Quartus或Libero SoC添加到当前MATLAB会话的系统路径中。

对于使用ISE设计软件Xilinx的FPGA板,运行:

hdlsetuptoolpath(“工具名称”,“Xilinx ISE”,“路径”,'C:\赛灵思\ 13.1 \ ISE_DS \ ISE \ BIN \ NT64 \ ise.exe');

本例假设Xilinx ISE可执行文件是C:\Xilinx\13.1\ISE_DS\ISE\bin\nt64\ ISE .exe。用您的实际可执行文件替换,如果它是不同的。

对于使用Vivado设计软件Xilinx的FPGA板,运行:

hdlsetuptoolpath(“工具名称”,“Xilinx Vivado”,“路径”,“C: \ Xilinx \ Vivado \ 2016.4 \ bin \ vivado.bat ');

这个例子假设赛灵思Vivado可执行文件是C:\赛灵思\ Vivado \ 2016.4 \ BIN \ vivado.bat。用您的实际可执行文件替换,如果它是不同的。

对于英特尔的董事会,运行:

hdlsetuptoolpath(“工具名称”,“阿尔特拉第四的二世”,“路径”,'C:\ Altera的\ 16.0 \的Quartus \ BIN \ quartus.exe');

这个例子假设在Intel的Quartus II可执行文件是C:\ Altera的\ 16.0 \的Quartus \ BIN \ quartus.exe。用您的实际可执行文件替换,如果它是不同的。

微芯板,运行:

hdlsetuptoolpath( '工具名称', '的Microsemi的Libero的SoC', '刀具路径', 'C:\ Microsemi的\ Libero_SoC_v11.8 \设计\ BIN \ libero.exe');

这个例子假设的Microsemi的Libero SoC的可执行文件是C:\ Microsemi的\ Libero_SoC_v11.8 \设计\ BIN \ libero.exe。用您的实际可执行文件替换,如果它是不同的。

5.打开fil_pid.mdl模型。

该模型包含具有基本的Simulink模块实现定点PID控制器。万博1manbetx这个模型也包含由该PID控制器以及作为输入激励期望的DC电动机位置控制的直流电动机模型。

现在运行这个模型,观察范围所需与实际电机位置。

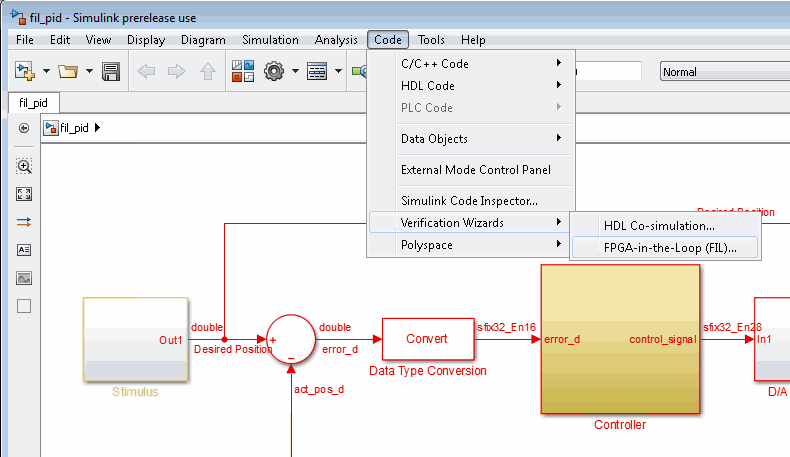

步骤4:启动FPGA-in-the-Loop (FIL)向导

通过执行以下操作启动FPGA-在环仿真向导:

从fil_pid模型窗口中的代码菜单,选择验证奇才 - > FPGA功能于环(FIL)...。

另外,您也可以在MATLAB命令提示符下输入命令filWizard。

filWizard

第5步:在FIL向导指定硬件选项

为FPGA开发板设置FIL选项。

1.指定如果向导将生成一个FIL Simulink模块或FILSimulation MAT万博1manbetxLAB系统对象。在这个例子中,选择万博1manbetx对于费尔仿真与万博1manbetxSimulink的。

2.董事会的名字,选择连接到您的主机的FPGA开发板。如果您的板不在列表中,请选择下列选项之一:

“获取更多的板…”下载FPGA板支持包(此选项启动支持包安装程序)。万博1manbetx

“创建自定义板...”创建FPGA板定义文件为您的特定FPGA电路板(此选项将启动新的FPGA董事会经理)。

3.选择模拟连接。可用连接方式是以太网和JTAG。并不是所有的主板都支持这两种连万博1manbetx接方式。

4.以太网连接只:如果你从192.168.0.x的改变了你的计算机的IP地址不同的子网,当你设置的网络适配器,或者如果默认板IP地址192.168.0.2是由其他设备使用,扩大高级选项和改变董事会IP地址根据以下指引:

子网地址,通常是板上IP地址的前三个字节,必须与主机IP地址相同。

董事会IP地址的最后一个字节必须是从主机IP地址的不同。

董事会IP地址不能与其他计算机的IP地址冲突。

例如,如果主机的IP地址是192.168.8.2,那么你可以使用192.168.8.3(如果可用)。不要换董事会MAC地址。

5.可选:如果您想更改默认(25MHz的)被测设备的时钟频率,可以扩大高级选项和改变FPGA的系统时钟频率(MHz)。

6.请点击下一个继续。

步骤6:在FIL向导中指定HDL文件

指定HDL设计在FPGA中实现。

1.单击Add并浏览到您在准备示例资源中创建的目录。

2.选择这些HDL文件:

Controller.vhd

D_component.vhd

I_component.vhd

这些都是HDL设计文件,在FPGA板上得到验证。3.在源文件表中,选中该复选框上的文件的行Controller.vhd以指定这HDL文件包含的顶级HDL模块。

费尔向导自动填充顶层模块名称与所选择的HDL文件的名称字段;在这种情况下,控制器。在这个例子中,顶层模块的名称相匹配,使您无需更改文件名。如果顶层模块名和文件名不匹配,你会手动更正该对话框中的顶层模块的名称。

请点击下一个继续。

步骤7:在FIL向导中检查I/O端口

FIL向导在Controller中解析顶级HDL模块控制器。获取所有的I/O端口并将它们显示在DUT中I / O端口表格解析器试图通过查看端口名称来自动确定可能的端口类型,并在端口类型下显示这些信号。

1.查看端口列表中。如果解析器分配一个不正确的端口类型为任何给定的端口,可以手动更改信号。对于同步设计中,指定一个时钟,复位,或时钟使能信号。在这个例子中,FIL向导会自动正确填写表格。

2.请点击下一个继续。

第8步:在FIL向导中设置输出数据类型

1.对于HDL输出control_signal改变数据类型至固定点,标志至签和分数长度至28。这将使生成的FIL块将FPGA待测设计(DUT)的输出信号设置为正确的数据类型。

2.请点击下一个继续。

步骤9:查看FIL向导中的构建选项

1.指定输出文件的文件夹。在这个例子中,使用默认的选项,这是一个名为子文件夹Controller_fil在当前目录下。

该总结显示FPGA项目文件的位置和FPGA编程文件。您可能需要使用高级的操作这两个文件。

2.请点击构建开始构建过程。

在生成过程中,发生以下操作:

在一个新的模型,产生命名为控制器A FIL块作为显示在下面的图中。不要关闭这个模式。

之后新的模型生成,该FIL向导打开命令窗口,其中FPGA设计软件进行合成,装配,布局和布线,时序分析,和FPGA编程文件的生成。

当FPGA设计软件过程完成时,命令行窗口中的一条消息让您知道可以关闭该窗口。关闭窗口并进入下一步。

第10步:建立模型

在fil_pid模型,更换控制器与新模型中生成的FIL块一起的子系统。修改后的fil_pid模型如下图所示:

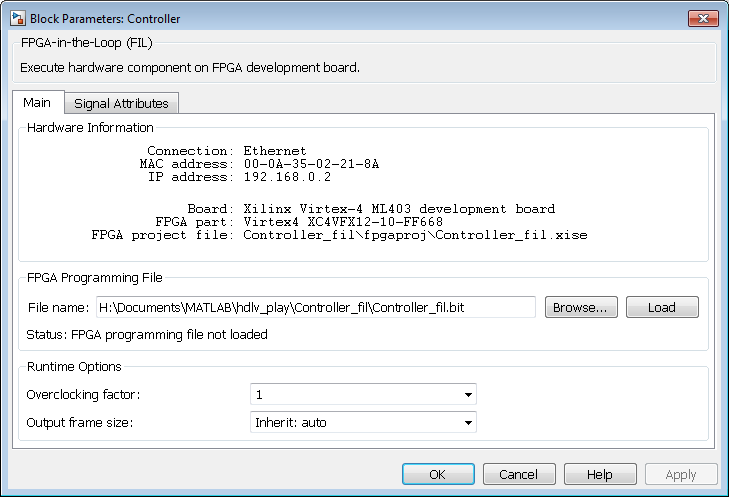

步骤11:计划FPGA

1.切换FPGA开发板功率在。

在fil_pid模型2.双击FIL块打开块屏蔽。

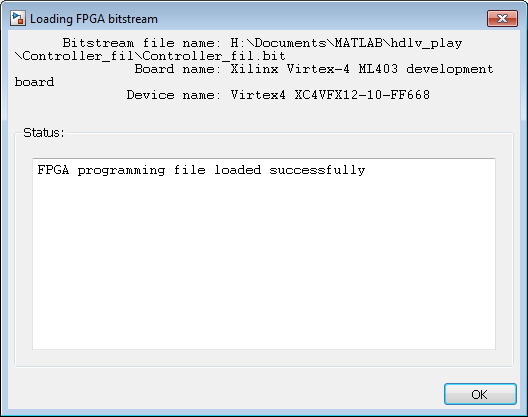

3.在opened block mask, click加载。

如果板被通过JTAG电缆连接到主机计算机适当地,一个消息窗口显示,以指示该FPGA编程文件被成功加载。请点击好吧要关闭该对话框。

4.只连接以太网:通过ping测试,可以测试FPGA板是否正确连接到主机。启动命令行窗口并输入以下命令:

C: \ mytest >期间。萍192.168.0.2

如果您在设置网络适配器时更改了板IP地址,请将192.168.0.2替换为板IP地址。如果千兆以太网连接已正确设置,您应该会看到来自FPGA开发板的ping应答。

步骤12:FIL块的检查参数

1.在FIL阻挡掩模,点击信号的属性标签。

2.验证数据类型的HDL信号的control_signal是fixdt(1,32,28)。如果不是,那就改变它。

3.点击好吧以关闭阻挡掩模。

步骤13:运行FIL

1.启动仿真的fil_pid模型。

2.仿真完成后,查看电机在范围内的期望位置和实际位置的波形。请注意,FIL模拟的结果应该与您在其中模拟的Simulink参考模型的结果相匹配万博1manbetx准备资源的例子。