主要内容

SerDes系统的设计与仿真

使用SerDes Designer应用程序设计和模拟SerDes系统

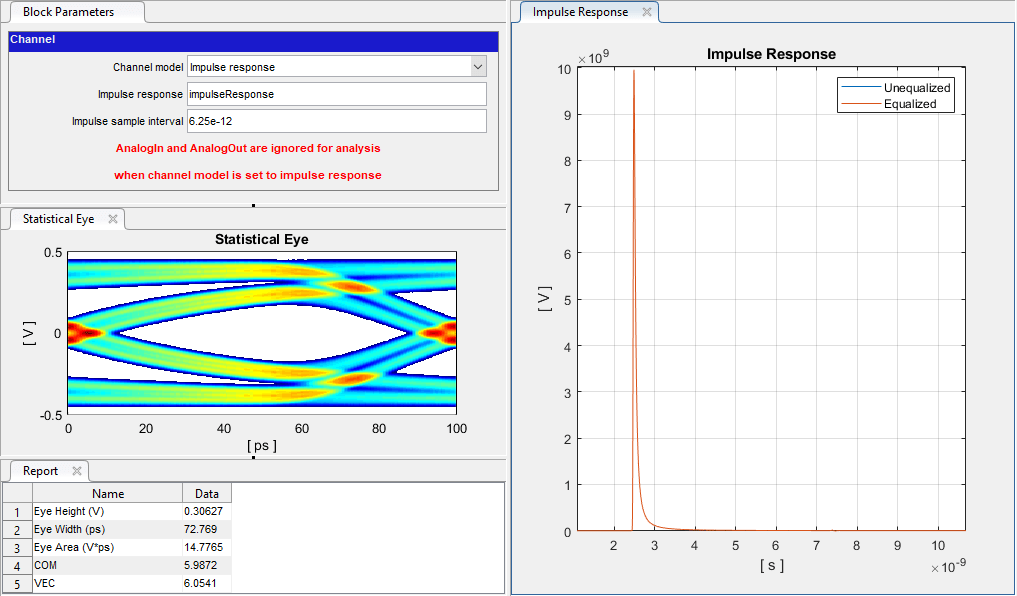

高速电子系统遭受信号退化的各种损害,如阻抗失配、衰减和串扰。使用SerDes工具箱™中的均衡和增益调制块,您可以补偿由有损信道引入的失真。

从塞德斯设计师应用程序,您可以设计顶级SerDes系统并执行统计分析。使用构建块和系统对象设计、配置、模拟和分析SerDes系统,包括发射机和接收机。

应用程序

| 塞德斯设计师 | 设计和分析用于导出的SerDes系统万博1manbetx,MATLAB和宜必思AMI |

阻碍

对象

功能

optPulseMetric |

优化例程的脉冲响应度量 |

prbs |

伪随机二进制序列 |

impulse2step |

阶跃响应来自脉冲响应 |

impulse2pulse |

脉冲响应的脉冲响应 |

步骤2脉冲 |

脉冲响应来自于阶跃响应 |

脉冲2脉冲 |

脉冲响应中的脉冲响应 |

脉冲状态 |

从脉冲响应看统计眼 |

pulse2pda |

从脉冲响应分析峰值失真 |

pulse2wave |

数据模式波形来自脉冲响应 |

wave2pulse |

来自数据模式波形的脉冲响应 |

主题

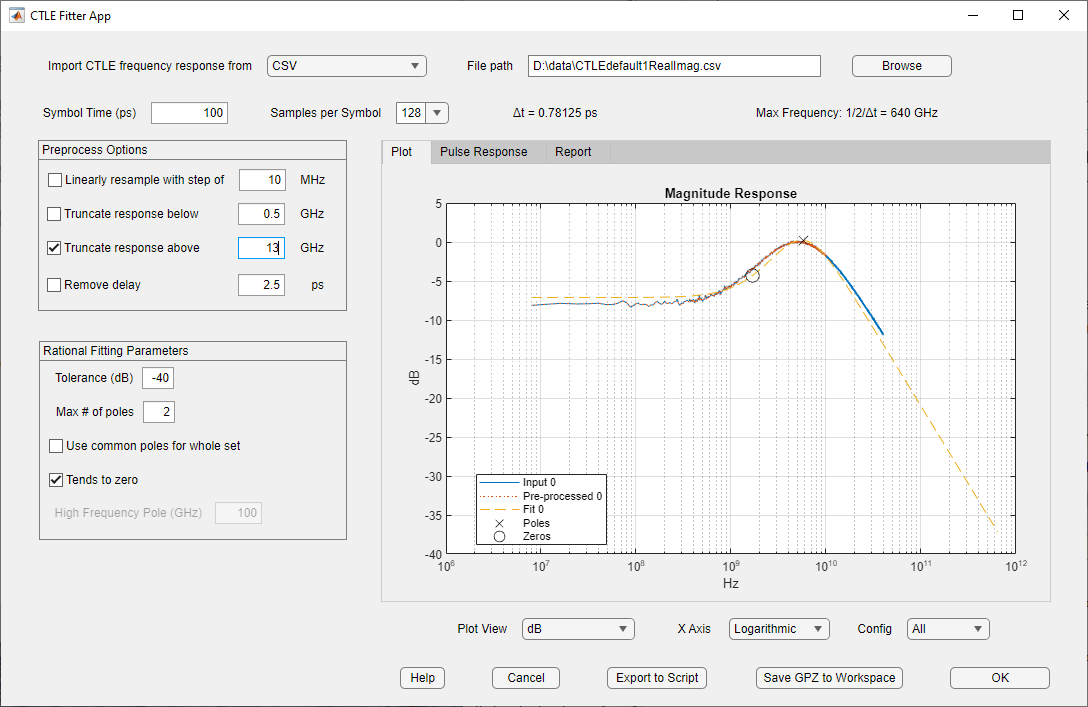

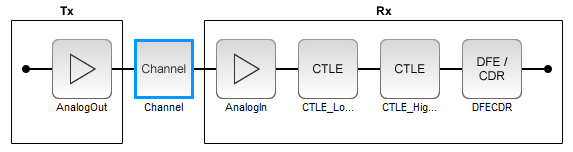

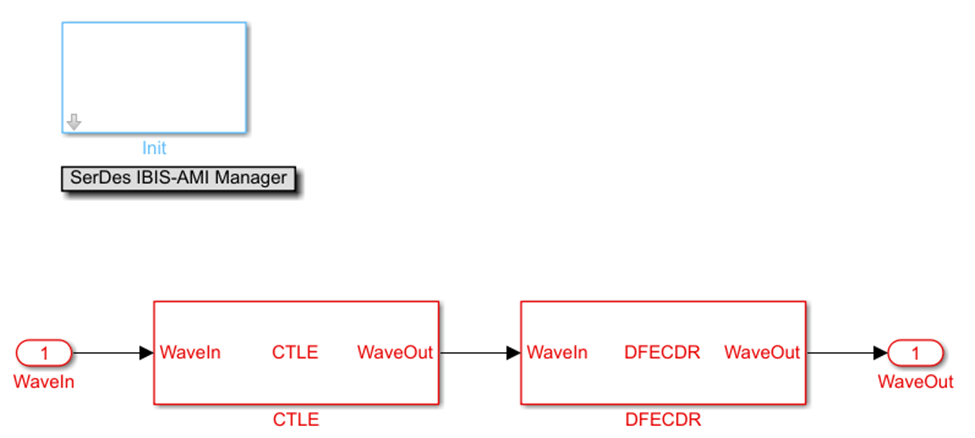

此示例演示如何使用SerDes Designer应用程序创建和分析SerDes系统,以及如何从Simulink®为发射机和接收机创建IBIS-AMI模型。万博1manbetx

构建SerDes系统的基本组件。

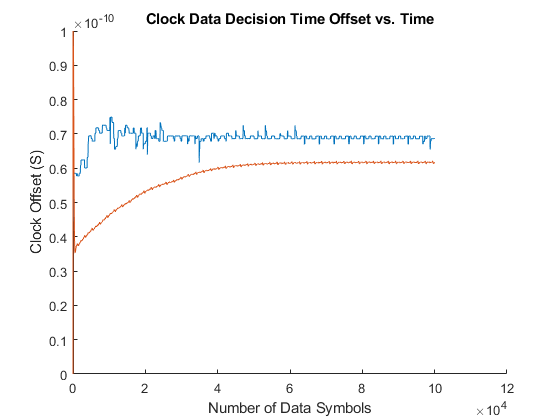

探讨一阶时钟数据恢复(CDR)的行为、控制和特性。

定制和探索SerDes系统的统计分析。

将抖动注入链路分析和均衡设计。

在兼容的Linux版本上生成共享对象。