FPGA数据捕获组件生成器

配置和生成FPGA数据捕获组件

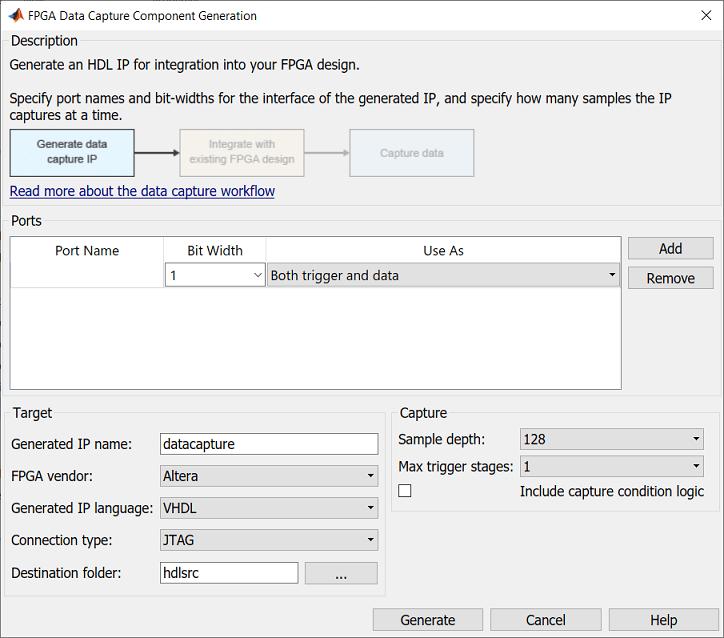

描述

这FPGA数据捕获组件生成器工具配置和生成组件,用于捕获FPGA上运行的设计数据。生成的组件从FPGA捕获信号数据窗口,然后将数据返回到MATLAB®或模拟万博1manbetx®。

要使用此工具,您必须具有现有的HDL设计和FPGA项目。为了捕获信号,HDL Verifier™生成了一个IP核心,您必须将其集成到HDL项目中,并与其余的设计一起部署到FPGA。

这产生此工具中的按钮生成这些组件:

HDL IP核心,用于集成到您的FPGA设计中。连接要捕获并用作触发器的信号,然后连接时钟和时钟启用。

生成报告,下一步的生成文件和指令列表。

设置捕获参数并将数据捕获到MATLAB工作区的工具。看FPGA数据捕获。

定制版本的

hdlverifier.fpgadatareaderSystem Object™提供了一种配置和捕获数据的替代,程序化的方法。万博1manbetx包含自定义的Simulink模型FPGA数据读取器堵塞。如果您有DSP System Toolbox™许可证,则此模型将捕获的信号流到逻辑分析仪波形查看器。否则,范围块显示信号。

有关工作流程概述,请参阅数据捕获工作流程。

打开FPGA数据捕获组件生成器

在MATLAB命令提示符下,输入:

生成FpgadatAcaptureip

要重新加载最新设计的参数,请使用恢复争论:

生成fpgadataCaptureip('恢复',真的);

参数

端口端口名称- 生成的IP上输入端口的名称

字符矢量|字符串标量

该名称不必匹配HDL文件中的信号名称。此名称用于:

生成的HDL IP核心上的输入端口。IP内部,此信号被路由到捕获缓冲区,或用作触发条件的一部分,具体取决于您的选择用于。

捕获的数据中的结构字段返回到MATLAB工作区

生成的simulink块上的端口万博1manbetx

触发器和数据类型参数编辑器中的信号表在捕获时间

数据类型:char|细绳

位宽度- 信号中的位数

正整数

该数字用于生成HDL IP端口定义,并有助于捕获缓冲区的总宽度。您可以在捕获时间指定捕获数据的数据类型。

笔记

如果您没有定点Designer™,数据捕获只能返回内置数据类型,例如UINT8。您必须为匹配内置数据类型的大小的生成的IP指定端口,即1、8、16、32或64位。我们建议定点设计人员启用任何大小的定点数据类型和捕获的信号。

用于- 如何在IP逻辑中路由信号

触发器和数据(默认)|数据|扳机

当您将信号指定为数据,将信号捕获到样品缓冲区并返回到MATLAB,但不能导致触发条件。当您将信号指定为扳机,可用于在捕获时定义触发条件,但未捕获并返回到MATLAB。您还可以指定信号用作触发器和数据。

生成的IP名称- 生成的组件的名称

数据抓取(默认)|角色向量

此名称用于生成的HDL IP核心,系统对象和Simulink模型。万博1manbetx

FPGA供应商- FPGA和软件供应商

Altera(默认)|xilinx

可用的供应商取决于您已安装的HDL验证支持软件包。万博1manbetxAltera有单独的支持软件包万博1manbetx®和xilinx®董事会。

生成的IP语言- 用于生成HDL IP核心的语言

VHDL(默认)|Verilog

选择用于生成的HDL IP核心的语言作为Verilog或者VHDL。

连接类型- 连接频道的类型

JTAG(默认)|以太网

选择连接通道的类型JTAG或者以太网。

笔记

以太网连接仅适用于Xilinx FPGA板。

目标文件夹- 保存生成文件的位置

HDLSRC(默认)|字符矢量|字符串标量

保存生成的文件的位置,指定为主机计算机上的文件夹的名称。

数据类型:char|细绳

样品深度- 每个信号捕获的样品数量

128(默认)|256|512|1024|2048|4096|8192|16384|32768|65536|131072|262144|524288|1048576

使用此参数在生成的HDL IP核心中指定内存的大小。内存的宽度是数据信号的总块宽度。

指定样本深度时,请考虑您在阅读数据时计划配置的窗口数量,因为它们共同影响每个捕获窗口的窗口深度。这窗口深度是个样品深度由捕获窗口的数量。指定捕获窗口的数量在里面FPGA数据捕获工具。

例如,如果样品深度是4096和捕获窗口的数量是4,然后每个捕获窗口的窗口深度为1024。

最大触发阶段- 提供触发条件的最大触发阶段数量

1(默认)|整数从1到10

使用此参数启用顺序触发。要从FPGA捕获指定的数据,请在多个阶段提供一组触发条件。

指定最大触发阶段,考虑您计划配置触发条件的最大触发阶段数。通过使用触发阶段的数量触发阶段的数量参数FPGA数据捕获工具。

例如,如果最大触发阶段是4, 然后触发阶段的数量可1,,,,2,,,,3, 或者4。