主要内容

FPGA数据捕获

从现场FPGA捕获信号数据

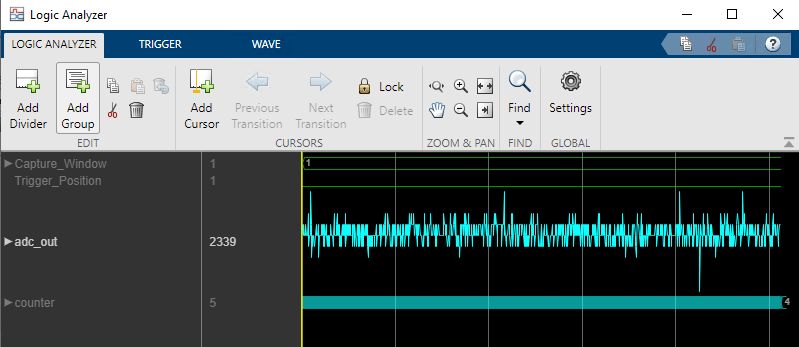

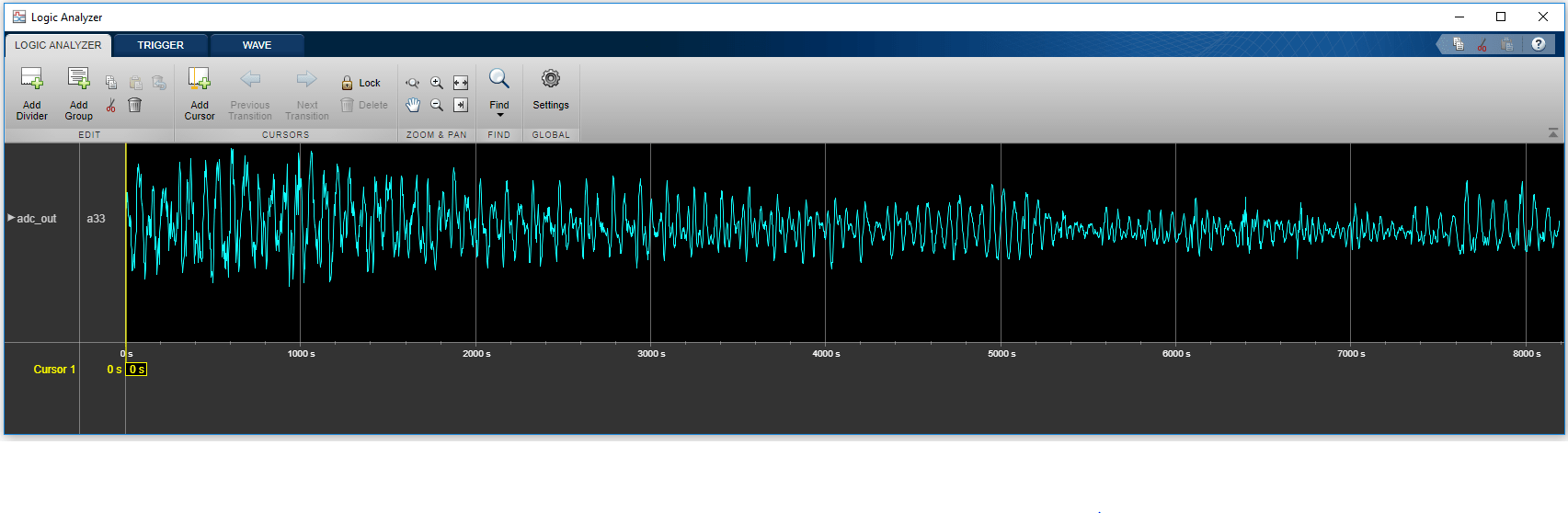

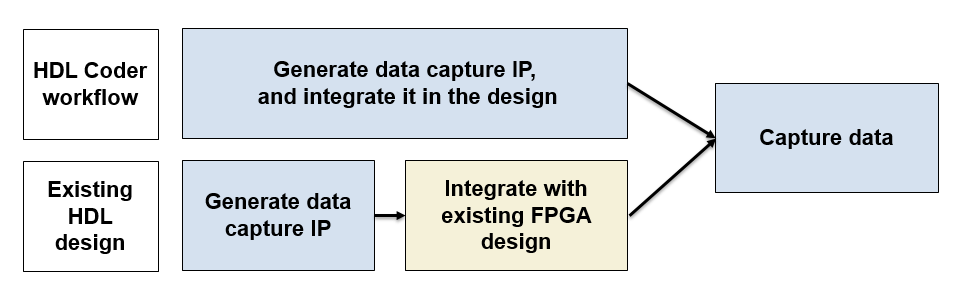

当设计在FPGA上运行时,使用FPGA数据捕获来观察来自设计的信号。该功能从FPGA捕获信号数据窗口,并将数据返回到MATLAB®或仿真万博1manbetx软件®.为了捕获信号,HDL验证器™生成一个IP核,您必须将其集成到您的HDL项目中,并将其与其余设计一起部署到FPGA中。HDL验证器还生成一个工具,System object™和Simulink模型,与FPGA通信并将数据返回到MA万博1manbetxTLAB或Simulink。

获取FPGA数据:

生成定制组件和IP核。为生成的IP指定端口名称和大小。这些端口连接到您想要捕获的信号,以及您想要使用作为触发器来控制捕获何时发生的信号。

将生成的IP集成到FPGA设计中,并将设计部署到FPGA板上。

使用生成的工具、System对象或Simulink模型来捕获数据进行分析、验证或显示万博1manbetx。您可以配置一个触发器条件来控制何时发生捕获。

看到数据采集流程.

工具

| FPGA数据捕获组件生成器 | 配置和生成FPGA数据捕获组件 |

| FPGA数据捕获 | 捕获数据从现场FPGA到MATLAB工作空间交互 |

功能

hdlverifier。FPGADataReader |

捕获数据从现场FPGA到MATLAB工作空间 |

块

| FPGA数据阅读器 | 捕获数据从现场FPGA到万博1manbetx模型 |