深度学习HDL工具箱

FPGA や SoC 上でのディープラーニング ネットワークのプロトタイピングおよび展開

深度学习HDL工具箱™ には、FPGA や SoC 上でディープラーニング ネットワークをプロトタイピングして実装するための関数とツールが用意されています。また、サポート対象の Xilinx®や英特尔®fpga socデバイスでさまざまなプラーニングネットワークするためため构筑済み済みののビットビットストリームが提供されれていいます。。プロファイリングツールツールツールおよび推定推定ををししししししししてを探求こと,プラーニングネットワークをすることができます。

深度学习HDL工具箱を使用すると、ディープラーニング ネットワークのハードウェア実装をカスタマイズし、任意の FPGA 上で展開するためのポータブルで論理合成が可能な Verilog®およびvhdl®コードを生成ます(HDL Coder™simuli万博1manbetxnk®が必要)。

詳細を見る:

プログラム可能なプラーニングプロセッサ

このツールはスケジューリングロジックによって制御制御泛用的畳み込みとと,全全结合结合层层层ををたたディープラーニングプラーニングプロセッサプロセッサプロセッサががが含ま含まれ深度学习工具箱™ を使用して開発されたネットワークの推論を FPGA ベースで実行します。高帯域幅のメモリインタフェースは、層および重みデータのメモリ転送を高速化します。

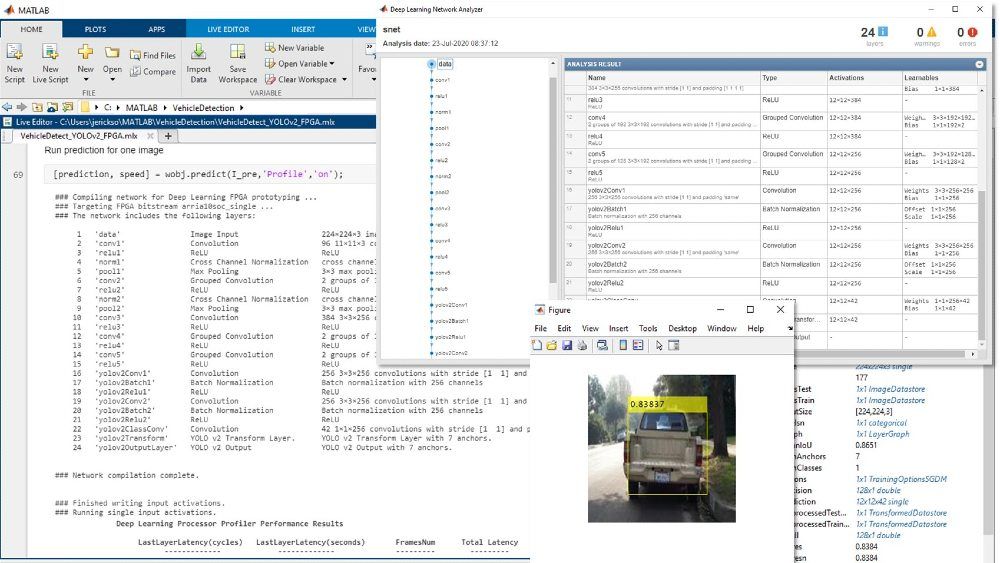

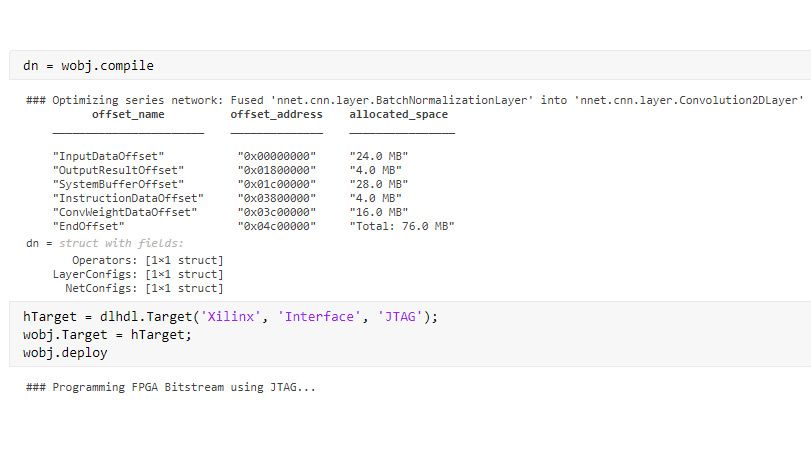

コンパイルと展开

ディープラーニング ネットワークを、ディープラーニング プロセッサで実行できるよう命令セットにコンパイルします。FPGA に展開し、デバイス上での実際の性能メトリクスをキャプチャしながら予測を実行します。

事前构筑のストリームを使用し始める始める

fpga开発开発キット用のなビットストリーム使用使用しし,,,,,,プログラミングプログラミングプログラミングプログラミングなしでネットワークををプロト

展开用のの作成

深度学习工具箱を使用,オブジェクトの検出分类のタスク用ディープラーニングプラーニングネットワークのの设计设计学习,解析解析を开始开始します。またまた,,フレームフレームフレームからからからからからから学习学习することもます。

fpgaに済みのを展开展开

学习済みネットワークのができたら,部署コマンドをて,イーサネットまたはまたはインターフェイスインターフェイスインターフェイスでディープラーニングをををををををににににプログラムします编译コマンドを使用して、FPGA を再度プログラムすることなく、準備した学習済みのネットワーク用の命令セットを生成します。

MATLABアプリケーションの一部として FPGA ベースの推論を実行

fpga,ベースベースベースベースののディーディープラーニング推论推论を含む含むアプリケーションアプリケーション全体全体ををを®Matlabのののの単一単一であるであるpredictコマンドは、FPGA 上で推論を実行し、結果を MATLAB ワークスペースに返します。

ネットワーク設計の調整

深度学习工具箱でをししででででしし。ますディープディープネットワークネットワークデザイナーデザイナー使用使用して,层层の追加,层层のの削除,,新しい接続

ディープラーニングの化

ディープラーニング ネットワークを固定小数点表現に量子化することで、リソースの使用量を削減します。Model Quantization Library サポート パッケージを使用して、精度とリソース使用量とのトレードオフを解析します。

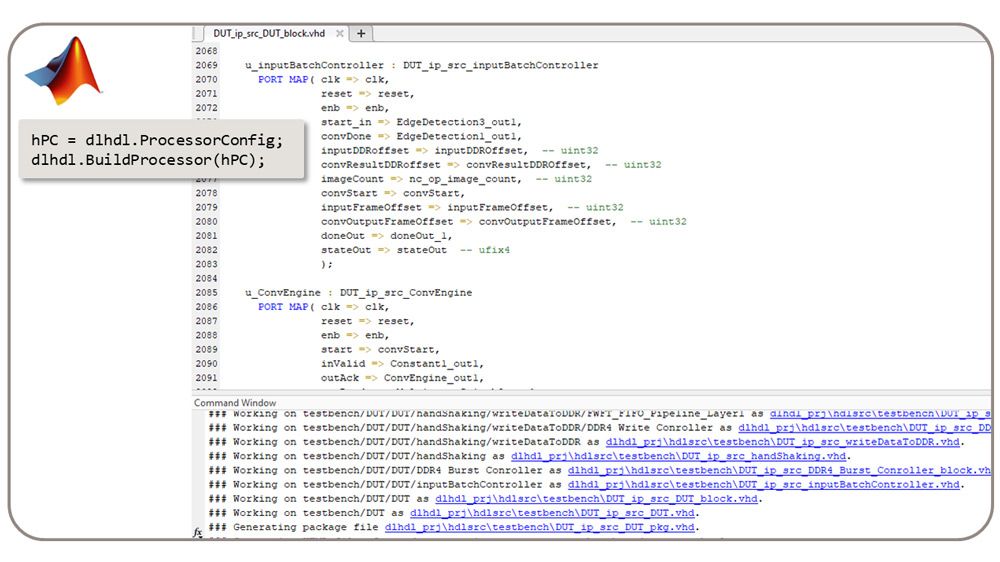

ディープラーニングプロセッサカスタム构成

并列スレッド层サイズなどディープロセッサを実装ためのハードウェアハードウェアアーキテクチャののオプションをを指定。

論理合成可能な RTL の生成

さまざまな実装ワークフローやデバイスで使用するために,高密度脂蛋白编码器を使用して,ディープラーニング プロセッサから論理合成可能な RTL を生成します。プロトタイピングと量産展開のために同じディープラーニング プロセッサを再利用します。

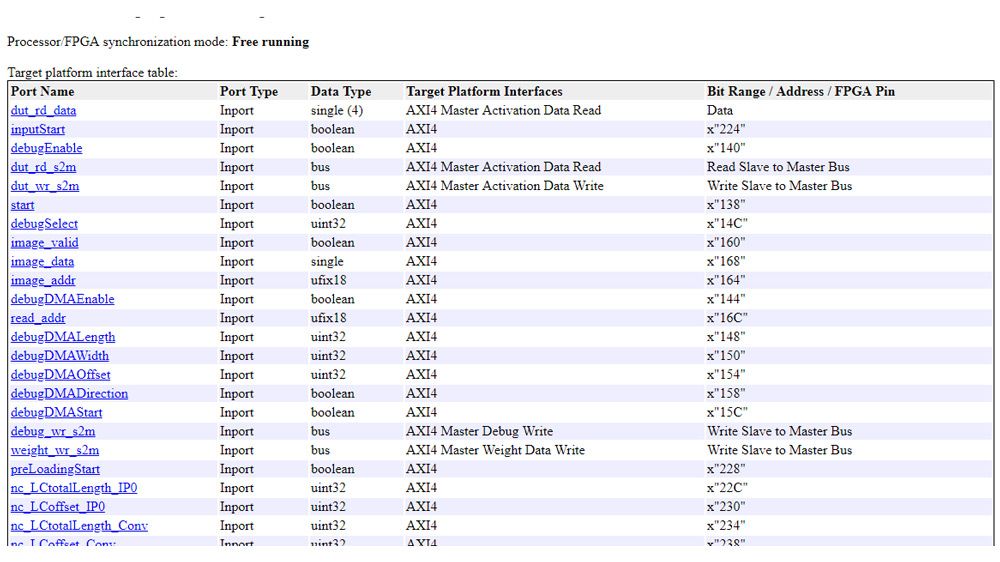

統合のための IP コアの生成

hdl编码器がプラーニング・からからからからをする场合,,リファレンスリファレンスリファレンス设计统合するための标准标准标准标准インターフェイスインターフェイスインターフェイスををを备え备え