设计多个像素 - 每钟FPGA应用程序

杰克erickson,Mathworks

处理每个时钟的多个像素并行地使FPGA和ASIC硬件能够处理4K,8K或高帧速率视频流。Vision HDL Toolbox™本身支持每个时钟处理万博1manbetx。Its Frame-to-Pixels and Pixels-to-Frame gateway blocks offer easy settings to switch the design’s inputs and outputs from one pixel at a time to 4 or 8 in parallel, and its built-in blocks such as image filtering and edge detection natively support this mode.

要开发自定义多像素/时钟算法,请在Vision HDL工具箱中的行缓冲区块存储足够的行,以形成一个邻域大小,您可以一次指定1,4或8个像素的列和控制信号。

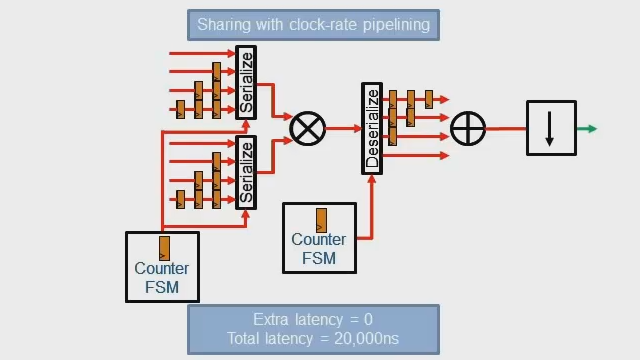

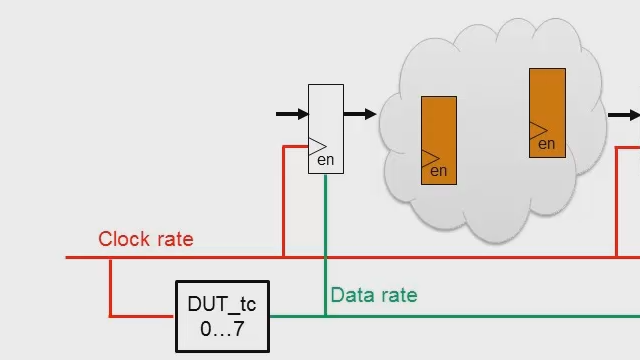

显示的设计是示例的自定义实现这个视频使用内置块。它显示如何使用行缓冲区创建四个并行邻域Windows,以由自定义设计的图像滤波器和边缘检测器处理。并行Windows显着重叠,因此该设计被架构以共享这些硬件资源。最后,它讨论了诸如寄存器管道插入的硬件微架构考虑因素,以及在满足延迟要求时减少乘数使用的方法。

相关产品s manbetx 845

您还可以从以下列表中选择一个网站:

如何获得最佳网站性能

选择中国网站(以中文或英文)以获取最佳网站性能。其他MathWorks国家网站未优化您的位置。