用神经网络校正ADC误差

Robert van Veldhoven, NXP Eindhoven

作为集成电路(IC)实现的模数转换器(adc)由于IC制造不完善而容易出错。不匹配的模拟元件,如晶体管、电阻和电容,会导致信号失真,例如,导致较差的总谐波失真(THD)。减少ADC误差的一种方法是通过使用更大的模拟组件来增强设计。这种方法改进了匹配,因此失真数,但需要更多的面积和功率。第二种方法是增加校准电路,但这也需要额外的硅面积,并增加成本和功耗,而且通常需要知道校准错误的确切原因。

在恩智浦埃因霍温,我的同事和我使用MATLAB设计和训练的神经网络后校正ADC错误®深度学习工具箱™。当在ASIC上实现时,该网络只需要ADC面积的15%,而在正常工作条件下消耗的功率大约是ADC的16倍。

神经网络的设计与训练

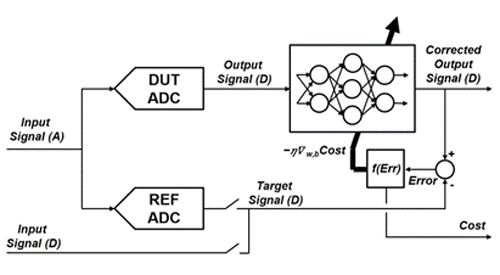

我们在实验室中通过向30个ADC样本(模具)提供参考信号并捕获数字输出来生成训练数据。另外10个样本被用于验证该网络。由于ADC误差同时受到温度和电压的影响,我们在9种不同的电压-温度组合下测试了每个样品,总共进行了360次测量。我们使用信号处理技术对数据进行预处理,然后使用ADC的测量数字输出值作为神经网络的输入。通过将校正后的输出信号与原始参考信号进行比较,可以更新网络系数(图1)。

图1。神经网络训练设置。

因为在项目开始时,我几乎没有神经网络的经验,所以我不确定网络需要有多复杂。我首先在MATLAB中创建基本的两层和三层网络,并改变每层神经元的数量。第一层和第二层的神经元使用sigmoid激活函数,输出层激活函数是线性的。所使用的代价函数是最小均方(LMS)代价函数。

在我们的数据集上训练了这些早期的网络配置后,我发现我可以通过将电压和温度测量作为预测指标来提高它们的性能。当我实现这一更改时,在很宽的温度和电压条件下,网络性能显著提高。

评估IC面积和功率

一旦我有了一个可以有效纠正ADC错误的神经网络,我想评估它需要多少硅面积和功率。为此,我生成了一个Simulink万博1manbetx®基于MATLAB的训练神经网络模型。然后,在生成VHDL之前,我使用定点设计器™量化了所有网络系数®代码从网络与HDL Coder™。我的同事通过HDL Verifier™cosimulation在Simulink中验证生万博1manbetx成的VHDL,然后使用Cadence®属综合设计。他还使用Cadence环境使用28纳米CMOS技术执行物理实现,生成功率报告,并计算使用的门的数量和这些门所需的面积。

分析结果表明,在面积和功率方面,神经网络可以以相对较低的成本纠正ADC误差。将信噪比提高约17 dB的网络只需要4600多个门和0.0084毫米的硅面积2来实现。ADC,测量0.06毫米2它的规模是整个网络的7倍多。有源时,网络消耗约15µW的功率,而ADC消耗233µW。

对于纠错电路,面积和功耗估计都被认为是可以接受的,但我相信,通过优化,我们可以提高这些数字。用于在VHDL中实现网络的工作流程非常简单,尽管我在机器学习方面相对缺乏经验。因此,设计和实现基于神经网络的电路所花费的时间并不比传统方法长,尽管我对这一过程并不熟悉。

提高可重用性和可移植性

在短期内,我们计划探索几种方法来验证神经网络在ADC错误校正中的使用。首先,我们希望更好地理解经过训练的网络是如何执行错误纠正的,以便我们可以将生产中意外行为的风险降至最低。其次,我们希望扩展我们的数据集。我们需要知道,如果我们使用100万个样本而不是40个样本,我们所获得的结果是否还成立。最后,我们想要衡量神经网络的可重用性。我们期望单个网络能够比传统设计更有效地补偿各种adc之间的不同误差,因为网络可以容纳广泛的传递函数。然而,我们需要进行进一步的测试来验证这一假设。

2021年出版的