费尔模拟

在FPGA硬件上模拟HDL代码万博1manbetx

- 库:

生成的

描述

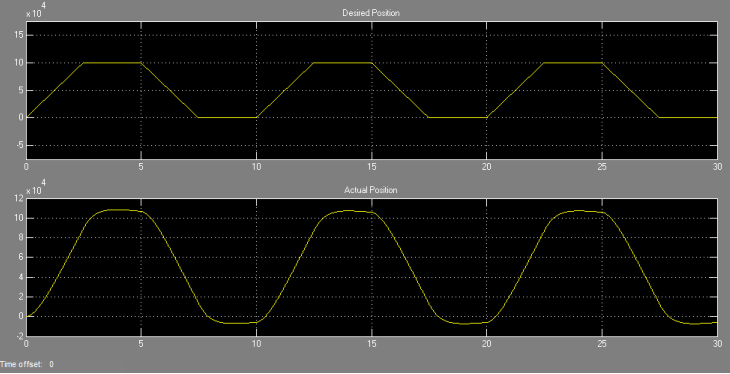

生成的FPGA-in- loop (FIL)模拟块是FPGA和Simulink之间的通信接口万博1manbetx®模型。它将硬件集成到仿真循环中,并允许它像任何其他块一样参与仿真。

你可以生成一个费尔模拟块从现有的HDL代码使用FPGA-in-the-Loop向导,或生成HDL代码和附带的费尔模拟块使用HDL工作流顾问。生成HDL代码需要HDL Coder™许可证。

生成和仿真工作流程请参见用FIL向导生成块.如果在FIL模拟过程中遇到任何问题,请参阅故障排除费尔帮助诊断问题。

您可以使用费尔模拟在正常、加速或快速加速模拟模式下运行的模型中的块。的费尔模拟在任何模拟模式中,参数都不可调。有关这些模式的详细信息,请参见加速模式如何工作(万博1manbetx模型).

港口

该块的端口对应于在FPGA上运行的HDL设计的接口。您可以配置信号的数据类型费尔模拟block返回到Simulink。万博1manbetx

输入

输出

参数

模型的例子

版本历史

在R2012b中引入