Gli esperti del settore e Gli ingegneri硬件实用MATLAB®电子万博1manbetx仿真软件®每一个原始的eseguire progetti ASIC di produzione。MATLAB仿真,puoi万博1manbetx:

- 基于硬件ASIC的Rifinire算法可消除通信误差

- 芯片上系统的动态模拟与阿司唑酮的活性对比

- 我们期待的是一个测试案例

- Generare RTL di alta qualità

" L 'ambient万博1manbetxe Simulink è ideale per L 'esplorazione dell 'architettura a livello di sistema。我们的模拟200 volte più快速的,完整的,完整的,不受影响的,有先例的模型Simulink所有必须的便利转换代码C e HDL,我同意的,提升scalabilità e riusabilità。"万博1manbetx

Ken Chen,法拉第

利用MATLAB的con ASIC SoC

模唑酮按丙唑酮ASIC

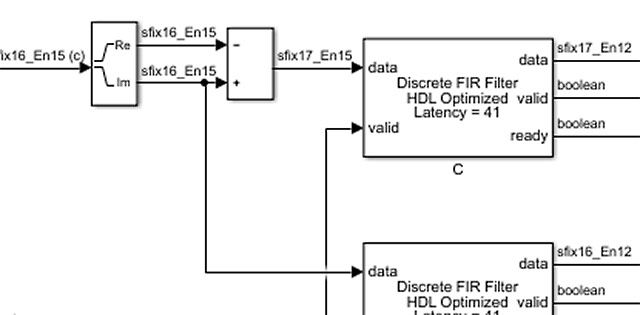

Aggiungil 'architettura硬件(13)altuo algorithm mo digitale。包括拉子午鱼(30:45),由联合国联合索più效率的提高,这是一个普遍的做法原住民,处女座(9:19)per prototiare più facility su FPGA。这是我的测试,我的算法,每一个相似的母体,连续的亲缘关系。

高密度脂蛋白编码器™genera Verilog o VHDL sintetizzabili direttamente da blocchi di funzioni MATLAB e 万博1manbetxSimulink pronti per HDL e grafici状态流®.这是我的秘密,我的秘密,我的秘密Prototipazione FPGA(20:51)在这个过程中。会议开始了Agilità e riusabilità这就是我们的硬件。

Ulteriori informazioni

Scopri i nosti prodotti

芯片上系统的模拟集成

modelella funzionalità digitali,analogiche软件在一个已确定的程序中,消除了一个错误,一个程序系统的错误,一个程序系统的问题。模拟记忆connettività国际esterna, oltre agli effetti di sistema operativo调度,利用率SoC Blockset™.

互动式自动测试用例是一个有效的系统万博1manbetx仿真软件测试™, e美国万博1manbetx仿真软件覆盖™Affinché le metriche soddisfino我需要。

我是这样的,我是这样的,我是这样的,我是这样的,我是这样的compatibilità我是这样的,我是这样的。

Scopri i nosti prodotti

期待着我的未来

高密度脂蛋白校验™riutility i tuoi ambienti di test MATLAB e S万博1manbetximulink per verificare il tuprogetto FPGA。

反对拉co-simulazione(35分), è可能eseguire自动camente il试验台di MATLAB和Simulink connesso al proget万博1manbetxto Verilog和VHDL eseguito在unsimulatore, da Mentor图形和Cadence设计系统。

电子竞技,类比,数字,组成部分SystemVerilog DPI(19)这是一种有规律的变化,有规律的变化,有规律的变化,有规律的变化Synopsys对此,Cadence设计系统o导师图形.

Scopri i nosti prodotti

Progetto ASIC di produzione

硬件usano MATLAB e Simulink / collaborare真主安拉realizzazione di pro万博1manbetxgetti FPGA e SoC / produzione / applicazioni无线,diexplazione Di immagini/视频,我控制着我的力量(24:20)e applicazioni批评每la sicurezza.

Esplora un 'ampia gamma di opzioni architecture, quindi utilzza le ottimizzazioni di sintesi complcompler di HDL Coder per raggiere i tooi obiettii di implementazione。自动属可消化che è可追溯的终端要求。Insieme al codiceRTL符合alle regole di progettazionee sintetizzabile, HDL Coder genera una varietà di interface AXI4 per un 'integrazione facile nel tuo SoC。

Ulteriori informazioni

Scopri i nosti prodotti