设计一个从FPGA到SoC块集处理器的数据路径:建模和仿真

埃里克•Cigan MathWorks

本视频是系列的一部分,演示了使用SoC Blockset™设计FPGA和嵌入式处理器之间的硬件逻辑数据路径的系统方法。应用程序经常在硬件逻辑和片上系统(SoC)设备上的嵌入式处理器之间进行划分,以满足吞吐量、延迟和处理需求。

学习设计和模拟包含FPGA和处理器算法以及内存接口的整个应用程序。您将看到如何使用SoC Blockset中的块来建模共享外部内存,以及如何使用SoC Blockset来测量不同形式的延迟,以及内存缓冲区中的数据丢失。

通过使用模拟执行这些分析,您可以比仅使用硬件时更好地了解设计。在硬件上实现之前,您可以发现吞吐量损失、延迟和样本丢失等问题。

在本视频中,我们将展示如何使用SoC Blockset建模和模拟硬件效果,当设计从FPGA到处理器的数据路径时。

通过在开发应用程序时模拟硬件效果,您可以评估总体性能,而不需要将应用程序加载到开发板上。此外,与使用开发板相比,使用模拟您可以对应用程序有更大的可见性,因此您可以更快地识别问题并测试潜在的解决方案。

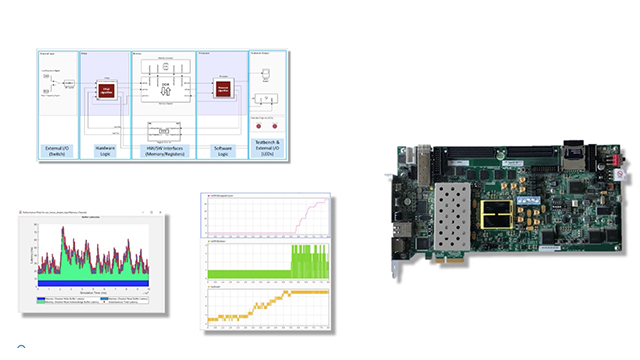

这是我们正在设计的应用程序的初始模型。它从外部来源接收一串正弦数据,将其分类为低频或高频信号,并照亮低频或高频检波器光。

我们将通过拨动开关来选择低频和高频信号进行测试。为了进行测试,我们将在FPGA中生成测试信号。FPGA对输入流进行过滤,然后将数据传递到缓冲区。这个初始模型使用了一个简单的理想缓冲区,它足以检验算法。处理器对数据帧进行操作,检测信号,并打开相应的检测器灯。

我们可以看到模型运行。在模拟中,我们可以在低频率和高频率的测试信号之间切换,我们看到探测器发光二极管亮起来。这个模拟证明了算法,但是现在我们想在DDR内存中合并缓冲的硬件效果,因为我们将在硬件中配置它。SoC块集包括帮助我们的块和模板。

考虑我们的应用程序的这个图表。FPGA以100 kHz的速率对测试信号进行采样。处理器每10毫秒处理一帧数据。由于数据从FPGA异步传输到处理器,我们在FPGA存储器和DDR存储器中插入一个FIFO。这里的虚线表示背压。这发生在内存缓冲区被填满时,可能需要更多的数据留在FPGA的FIFO中,直到缓冲区被刷新。

以下是设计必须满足的两个要求:

- 允许的最大延迟是100毫秒

- 我们不能在10000个样本中减少超过1个

当我们试图满足这些要求时,我们将关注两个参数:帧大小和缓冲区的数量。

我们使用SoC Blockset中的块来更准确地建模该设计的体系结构。

- 内存通道块通过DDR共享内存传输数据。在该模型中,内存通道模型实现了从FPGA到处理器通过DMA的AXI4-Stream协议。

- 内存控制器块仲裁并授予对内存的访问权。

- 寄存器通道模拟了从处理器返回到FPGA的通信,我们看到FPGA块通过其输出引脚驱动led。

首先,我们使用800个样本的帧大小,每个样本消耗4字节。我们还指定内存区域将由11个缓冲区组成。我们设置了存储通道块的参数并进行了仿真。

在模拟过程中,我们可以切换输入信号在低频和高频信号之间。我们可以看到来自处理器的数据输出信号和频率的变化,我们可以看到指示灯相应的变化。我们运行了100秒的仿真时间,这个模型已经运行到完成。

我们打开内存通道块,它用于逐帧测量延迟。如图所示,在进行了几秒钟的模拟后,延迟达到了100毫秒的范围。允许的最大延迟是100毫秒,所以这个设计与延迟需求相差不大。既然我们已经接近需求了,我们就暂时继续吧。

另一项要求是,每10,000个样本中不能丢弃超过1个。使用SoC Blockset,模型被仪表化,因此我们可以确定样品是否正在被丢弃。我们可以从上面的图表中看到,在模拟过程中大约3秒后,缓冲区使用率开始增加,然后增加到5.5秒左右。中间的图表描绘了FIFO的使用情况,底部的图表描绘了被丢弃的样本数量。

大约5.8秒时,先进先出系统开始平稳地丢弃样本。到100秒结束时,将近900个样本被丢弃,我们可以看到每10秒,大约有100个样本被丢弃。这与万分之一的要求相差无几。因为这个设计不符合任何一个规格,让我们尝试改变内存配置。

我们将增加帧大小从800到1000个样本,并减少缓冲区的数量从11到9。然后我们用新的参数重新运行模拟。

仿真完成后,我们可以打开内存通道块。在这种情况下,延迟达到23秒的峰值达到模拟,其中达到约78毫秒的延迟。请记住,最大允许的延迟是100毫秒,所以现在我们非常安全地在这个限制下。

然后我们再次检查,看看我们是否在10,000个样本中丢弃少于1个。当我们看看相同的三个变量时,我们可以看到没有任何样品被丢弃。这意味着我们现在有一个符合我们两个要求的设计。

现在,我们已经使用SoC Blockset模拟来确定帧大小和缓冲区的数量,我们准备在FPGA板上实现硬件设计,我们可以执行进一步的测试SoC Blockset来验证我们的模拟结果。

总而言之,我们使用SoC Blockset以硬件效果来增加算法模型,这样我们就可以使用模拟来看看不同的帧大小和缓冲区数量是如何影响性能的。

通过模拟算法的硬件架构,我们能够在硬件上实现之前发现延迟和样本丢失等问题。

相关产品s manbetx 845

了解更多

你也可以从以下列表中选择一个网站:

如何获得最佳的网站性能

请选择表现最佳的中国网站(中文或英文)。MathWorks的其他国家网站并没有针对您所在位置的访问进行优化。