使用MATLAB和Simulink开始软件定义无线电万博1manbetx

诺姆·莱文,MathWorks公司

Robin Getz,模拟设备

Luc Langlois, Avnet电子营销

从加入The MathWorks公司,ADI公司和安富利工程师谁将会显示软件定义无线电单一的硬件/软件开发和部署环境。使用MATLAB®和Sim万博1manbetxulink®,用户可以从设计和模拟通信算法到生成针对Xilinx的产品实现®Zynq®-7000所有可编程SoC和ADI公司AD9361 RF收发器雅居乐™。

在我们的介绍中,我们将演示如何:

- 建模和仿真无线电设计

- 验证在仿真算法与流RF数据

- 在基于ZYNQ-硬件与HDL和C代码生成部署的无线电设计

• 请拜访http://www.analog.com/adrv9361,或联系最近SOM订购信息您当地的ADI代表。

您好,欢迎来到网络研讨会开始使用软件定义无线电设计使用MATLAB和Simulink。万博1manbetx我的名字是诺姆·莱文,技术营销FPGA和SSE解决方案在这里MathWorks公司。万博 尤文图斯我会在此演示文稿由罗宾·盖茨从安富利ADI公司和吕克·朗格卢瓦被加入。通过此次研讨会的最后,我们希望您了解SDR设计的新的工作流程,使您可以从系统仿真到生产部署在一个硬件/软件工具环境中的元素。

我们也想让你知道在哪里可以找到资源,帮助您与您的无线实施项目。我们将在本次网络研讨会将涵盖的主题包括模拟和RF信号链的模拟,建模和通信算法仿真,与现实世界的数据算法的测试和验证,最后,通信系统的部署,硬件原型和生产。

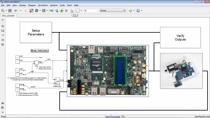

这个工作流程可以应用于许多基于zynq的SDR平台,包括来自Avnet的模块上的新的PicoZed SDR系统,它允许您使用相同的硬件从开发到生产部署。对于设计到原型部署,该工作流程也可以应用到其他开发平台,包括Zynq-7000所有可编程SoC,以及模拟设备AD9361射频敏捷收发器。

现在我将把工作交给Avnet的Luc Langlois来描述新的PicoZed SDR平台。

软件无线电的所有设计者们你们好。我是Avnet Global Technical Marketing的Luc Langlois,在这里介绍我们最新的PicoZed SDR software-defined radio,它是一个可生产的系统,在模块上,体积小,功耗低。

该系统包括在ADI AD9361 RF敏捷收发器,赛灵思ZYNQ-7000的所有可编程系统芯片,并且可以运行嵌入式Linux。我们与业界领袖ADI公司,MathWorks公司和赛灵思公司密切合作,创建模块,集成传输和设备的一个扑克牌大小接收功能的生产就绪系统,由2种MIMO配置,以及频段实现270兆赫到6千兆赫。它可用于发展,最终,插入右到最终产品。

应用程序包括便携式敏捷无线通信、公共安全无线电、点对点通信、femtocell和picocell基站以及便携式仪表。

PicoZed SDR SOM设有赛灵思7Z035 ZYNQ SOC器件,在ADI 9361 RF收发信机,DDR 3低功率的一千兆字节,四路SPI非易失性存储器256兆位,USB 2.0在旅途中,以太网,microSD卡,和204用户I / O都在SOM。充分开发套件添加一个FMC载体卡,天线,电源和电缆。在picozed.org/sdr更多信息和订购。

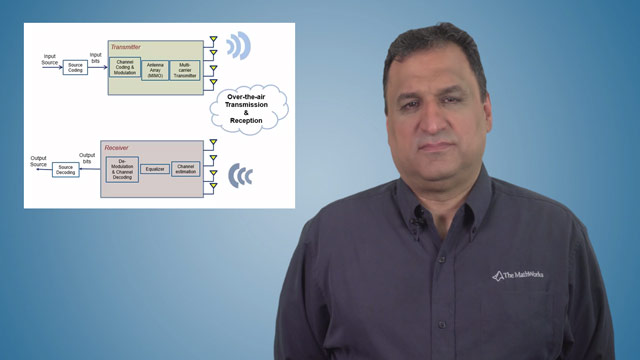

谢谢,卢克。现在我们已经确定了目标硬件,可以开始设计过程了。这个简单的方框图显示了软件定义无线电系统的主要元素。正如我们在对PicoZed SDR SOM的描述中看到的,硬件包括一个射频收发器,来自模拟设备的AD9361,以及一个基带处理引擎,Xilinx Zynq-7035全可编程SoC。我们已经添加了另一个块、测试和验证,以展示如何将您的开发工作流集成到您的硬件上。

在这个研讨会,我们将采用基于模型的设计,还是自上而下的方法,对系统的开发。在这种方法中,我们先从软件仿真MATLAB和所有主要的系统组件的Simulink中,然后迁移这些元素的硬件,因为它们是开发和验证。万博1manbetx我们将通过以验证我们的基带处理算法和整体系统概念我们在MATLAB和Simulink整个信号链建模开始。万博1manbetx

然后,我们将使用真实的流数据在Simulink中验证和优化我们的算法。万博1manbetx一旦我们的算法通过真实数据进行了验证,我们就可以将其部署到原型环境中的硬件中,并在MATLAB和Simulink中进行实时参数调优和分析,以验证其性能是否达到目标。万博1manbetx最后,我们将把我们的算法部署到一个独立的系统上,用于生产实现。

现在,让我们从软件模拟开始,更详细地研究这些步骤。在这部分工作流程中,我们将纯粹在Simulink环境中工作,模拟从RF收发器开始的整个信号链。万博1manbetx我们的系统将使用模拟设备AD9361射频敏捷收发器,这是Robin从我们现在描述的模拟设备中获得的。

我们今天要讲的是9361 9364。这是一个完整的射频收发器。它是70兆赫,6千兆赫的调谐范围,200千赫兹到56兆赫的频道带宽。所以它是非常宽的频带,非常宽的调谐范围,非常集成。所以你在屏幕上看到的所有东西都集成到一个10乘10的包中,两个完整的接收链,两个完整的9361传输链。

因此,我们有什么是从单晶完整的LO产生,所以它推动我们的VCO。这反过来又推动了我们收到的PLL,发射锁相环,基带的PLL,完整的ADC / DAC的数字滤波器,数字接口,启用状态机,可以在多种不同的模式进行操作,从快速攻击一个非常复杂的自动增益控制,攻击速度慢,为手动模式。

其中一件事是,当你讨论像这样的集成系统时,你能达到离散解的性能吗?我们可以在这种设备中因为我们在设备内部做了数字和模拟校准和校正。

如此反复,如果你看的部分,它有它的可编程的许多阶段。而刚刚从模拟接收路径,我们有阻抗放大器,我们有我们的低通滤波器,我们可以用来划分ADC率下降一半我们的乐队。我们有可编程的FIR滤波器。而当我们在寻找的东西,我们需要了解与伟大的可编程变大的混乱。

所以,当我们谈论1000点的方式,或1000个谍配置寄存器,它基本上是999个办法让它错了,只有一个办法,实际上使其改正,正常工作,并得到你要找的性能。

谢谢,罗宾。为了帮助你做对,编程AD9361, MathWorks,结合模拟设备,建立了一个行为模拟模型,让RF和系统设计者能够看到整个RF信号链。这使您能够准确地了解算法在实际硬件环境中的执行情况。

这是一个真正的多域的系统级模型准确表示AD9361的行为,使所有的实际硅提供给他们的可编程功能的用户访问。我们不会在这一时间的探索太多深入的模型,但是我们会提供一个链接到更详细的信息。对于这个例子的目的,我们将着眼于刚刚收到AD9361收发器模型的路径。

在这里可以看到所有的设备的主要部件在Simulink被表示,结合状态的流程图,以自动增益控制模型,并且SIM RF块到收发器的RF部分进行建模。万博1manbetx为了便于讨论,我们将使用QPSK接收机作为我们的例子处理算法。让我们来看看我们如何能够在处理模型。

这里我们在Simulink中运行QPSK系统。万博1manbetx如你所见,我们的QPSK发射机直接连接到我们的QPSK接收机。这是你在设计过程中要开始的地方——纯算法模拟,理想的资源提供你的模型输入。

现在,让我们把我们的模型的一个步骤,让我们引入AD9361 RF收发器的模型到我们的系统,我们可以看到在我们的模拟信号装置的效果。现在,我们将阐述我们的系统模型,包括AD9361的接收器部分的模型,与输入信号进行一些对照一起,像另外一个连续波源,以更好地模拟潜在的现实实施。

我们仍然在使用,我们在过去的例子中看到相同的QPSK接收器模型。但是,现在我们可以看到收发器设置和系统条件的变化如何影响算法的性能。例如,我们可以调整QPSK传输相对于我们的CW功率我们的力量的水平,看看它如何影响我们的接收信号。

查看AD9361接收器内部,我们开始了解设备的复杂性,但您也获得了检查整个信号链的能力——这是仅靠硬件无法做到的。同样,我们将为您提供关于仿真模型的更深入讨论的链接,但是我想强调一下这个模型的一些主要部分,包括AGC,它是用Stateflow中的状态图实现的。你的增益表,你有能力编辑。再一次,提供设备的精细控制。你的射频接收部分,在那里你可以深入到你想要的去调制器。这些都是从我们的SIM RF库模块中建模的。然后几个可编程滤波器在接收端,和我们的数字下变频器。

而所有这些过滤器是通过使用AD9361过滤器向导,这是一个MATLAB应用程序,您可通过ADI公司的配置。所以过滤器向导,可以指定所有的滤波器参数,然后就可以下载到你的模型微调装置的操作。

现在我们已经看到了我们在模拟算法工作,仿真数据,我们现在看,以验证使用真实数据我们的算法的运行从AD9361到MATLAB和Simulink流。万博1manbetx我们可以把这个操作,作为无线的半实物仿真。使用来自通信系统工具箱ZYNQ SDR万博1manbetx的支持,你可以从AD9361到MATLAB和Simulink流数据。万博1manbetx该支持包万博1manbetx,可以控制收发器参数。

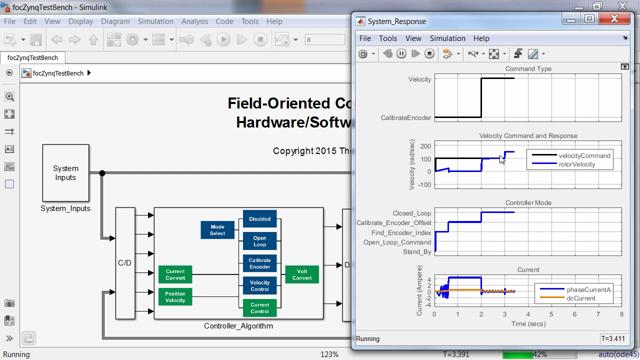

在工作流的这一部分中,Zynq上没有运行任何代码。所有的基带处理都在MATLAB和Simulink中进行,ARM核心放在Zynq封装数据上,通过以太网传输。万博1manbetx这是我们的QPSK接收器,它看起来非常像我们在上一个例子中看到的QPSK接收器模型,只是现在我要把它连接到这个SDR接收器块上,而不是连接到AD9361的模型上。这个SDR接收器块是用来建立Simulink和Zynq目标硬件之间的通信链路的。万博1manbetx

我要做出一个改变这种模式。这是我们的航运例子,它不拿出一个星座图。所以我打算从我们的通信系统工具箱星座图添加。因此,我们将带来在,所以我们才可以看到我们的数据,我们的数据的另一个可视化。我们也将能够传送从我们发送的消息 - “!你好,世界”消息我们在前面的例子中所看到的,当我打开了我的MATLAB画面。

我们现在要做的是运行这个模型。在房间的另一边,我有另一个基于zynq的SDR工具包,它运行一个QPSK发射器,我们将看看能否捕捉到我们已经拥有的数据。如果我打开我的MATLAB窗口,我们可以看到正在被这个QPSK接收器传输和接收的Hello世界。

在本例中,我们没有在Zynq设备上运行任何QPSK算法。该算法仅在Simulink中运行,数据来自AD9361。万博1manbetx我们可以看到现在发生了什么,当我关闭我的发射机,以显示我们实际上正在接收真实的数据直播。我把发射机关掉。我们可以看到我的星座消失了。我不会再收到任何东西了。

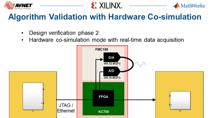

现在,我们的算法已被证实与真实的数据,我们可以生成HDL代码瞄准的ZYNQ SoC的可编程逻辑来实现我们的设计。下面是一些需要采取从您的Simulink设计产生良好的HDL代码的步骤。万博1manbetx

首先,你需要创建一个浮点参考。转换浮点参考定点数据类型。阐述你的设计更高效的硬件实现。并综合HDL代码,然后探索各种HDL优化和验证代码。

第一步我们已经完成。这个演示过程中,我们一直在寻找的QPSK接收模式是我们的参考实现。我们现在需要做一些修改,使之更HDL友好。

为了在FPGA上实现我们的模型,我们首先需要将其转换为使用定点数据类型。MathWorks在定点设计器中提供了许多工具来帮助自动化和流线化此任务。完成后,您将希望模拟模型的定点版本,以查看它如何与您已经完成的浮点模拟匹配。

使模型HDL友好化的另一个关键步骤是转换我们处理传入数据的方式,到目前为止,大部分数据都是基于框架的。我们需要转换体系结构,使用基于示例的处理,并查看模型的元素,我们可能希望修改这些元素以使其对硬件更加友好。再次,重新模拟并与您之前的模型详细说明进行比较,以保持持续的验证。

这张幻灯片显示了我们可以在QPSK发射机做农产品流数据。并且在接收器上,我们可以修改像更多的硬件实现友好的架构粗略的频率补偿元件。所有在HDL-QPSK优化模型,结果。

在这里,我们有我们的HDL-QPSK优化接收机例如,在更多的硬件友好的方式实现的各种块。现在,我们有我们的模型的HDL的版本,我们现在可以生成HDL代码和目标部署。第一个步骤是生成HDL代码,我们将做到这一点使用HDL流程顾问。

这是我的工作流程HDL顾问,和它要带我穿越的过程中一步一步生成代码为我的模型。我已经设定我的目标和我的SDR方案;在这种情况下,我们是要定位SDR平台。下一步是要检查我的模型,以确保它是有效的,使用有效的块HDL代码生成。

所以,我们要做的就是我们正在经历所有这些模型检查时,仅运行,以确保一切都很好。现在,我们的模型检查完成后,我们就可以生成HDL代码。有很多的,我们可以从优化选择的选项。我们有报告说,我要选择,使我们可以看看我们的一些代码生成的事后特征的一些基本选项。现在,我们去和我们的生成HDL代码。

我们的代码生成现已完成。让我们来看看一些报告,我们已经要求的。因此,我们可以得到的第一件事情是,我们已经生成的代码模块的代码生成报告。这是伟大的。这告诉你所有关于你如何瞄准装置。你有资源报告在一个很高的水平向您展示有多少你的FPGA的,大概,你要利用。

我们还能够跟踪代码。它的美妙之处在于你可以从一个代码到另一个模型,从一个模型到另一个模型,这样你就可以得到完整的可跟踪性。如果你想看看你的HDL是什么样子,你可以点击这些超链接中的任何一个,它会带你回到生成代码的模型中的代码块。

类似地,您可以转到模型中的任何块,并导航到由该块生成的代码。这在做设计评审之类的事情时非常方便;或者,如果您不得不担心标准遵从性,这是一个可跟踪的工作流。

接下来的步骤,很遗憾我们没有时间在这个演示中展示。这些就是在Simulink中创建和合成一个Vivado项目,然后创建IP核,用于Vivado中的PicoZed SDR参考设计。万博1manbetx这使用我们的IP核心生成工作流来针对Zynq-7000 SoC。

我们还有很多优化HDL性能的选项。当我们生成HDL代码时,我们选择了所有的系统默认值。在实际情况中,您可能会开始使用所有缺省值,查看应用程序的运行速度,然后开始查看各种速度和区域优化,以获得最佳的HDL代码生成。

我们真的只能够在SDR设计过程中的表面划伤在这次讨论中。如果您有兴趣更深入的培训,安富利,与MathWorks公司一起,ADI公司,公司和Xilinx公司正在提供一系列为期两天的动手研讨会将在部分城市呈现世界各地。这些研讨会将带您在整个设计过程中,我们使用MATLAB,Simulink和该PicoZed SDR SOM在此次网络研讨会概述,从设计到生产就业。万博1manbetx

更多信息,请picozed.org/sdr。如果您没有看到预计在您所在地区的研讨会,请要么接触当地的安富利代表,或者您也可以在fpga_expert@mathworks.com与我们联系,讨论替代的训练安排。

要充分认识HDL代码生成过程和SDR的设计过程中,有一些话题,我们可以进入更深入。这些链接将被发送到在后续的电子邮件全部网络研讨会注册。他们包括ZYNQ工作流程和ZYNQ培训资源,在AD9361模拟模型进行更深入的分析,对IP核生成的工作流信息。与往常一样,你可以在fpga_expert@mathworks.com与我们联系。谢谢。

记录:2015年10月20日