生成SystemVerilog断言和功能覆盖

SystemVerilog DPI组件生成和通用验证方法(UVM)测试台架生成工作流使您能够重用Simulink万博1manbetx®结果的SystemVerilog中的验证模型。万博1manbetxSimulink模型验证块等断言(万博1manbetx模型)或检查动态下界(万博1manbetx模型),并呼叫验证(万博1manbetx仿真软件测试)语句在生成的SystemVerilog中创建错误检查和功能覆盖点。

当一个Simu万博1manbetxlink断言或验证调用失败时,默认生成SystemVerilog错误。当其中一个成功时,它生成一个SystemVerilog覆盖点,记录PASS结果。断言和验证语句行为可以使用SystemVerilog命令行参数和HDL Verifier断言块定制。有关自定义的详细信息,请参见定制的断言.

创建一个Simul万博1manbetxink测试台模型

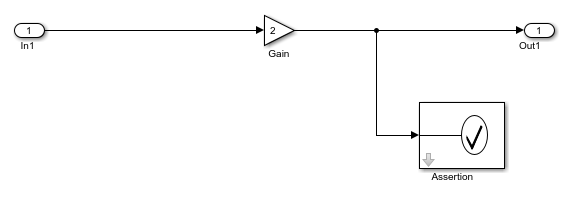

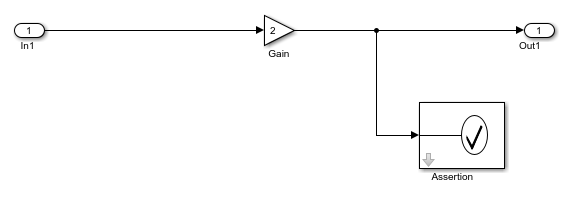

在Si万博1manbetxmulink中,为被测设备(DUT)创建一个模型,然后为该模型创建一个测试台。您可以使用来自Simulink / Model Verification库的断言块和包含万博1manbetx验证来自Simulink Test库的语句,万博1manbetx例如:

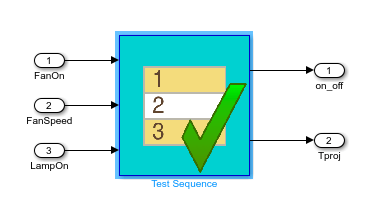

创建Simul万博1manbetxink测试序列

在您的测试台架模型中,包括验证语句,添加一个或多个这样的块:

要创建和编辑测试步骤,请使用测试序列编辑器(万博1manbetx仿真软件测试).在测试序列中,使用验证语句来评估模拟,如中所述测试序列和评估语法(万博1manbetx仿真软件测试).

的验证声明和测试序列块表示Simulink中的时间检查。万博1manbetx在生成SystemVerilog DPI组件时,时态逻辑位于生成的C代码中。SystemVerilog包装器包含在违反验证条件时触发的即时断言。

包括Simuli万博1manbetxnk模型验证块

您还可以从Simulink /中包含这些断言块万博1manbetx模型验证(万博1manbetx模型)图书馆。

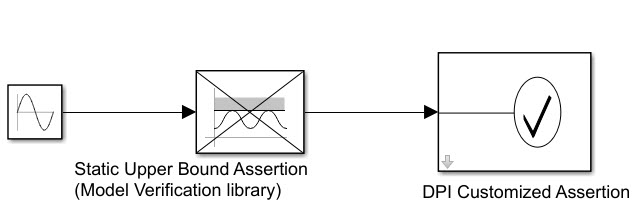

此外,您还可以包括HDL验证器断言块来创建可定制的断言。这是一个使用HDL验证器的例子断言块,看从Simulink生成本机SystemVerilog断言万博1manbetx.

在SystemVerilog中,每个模型验证块和验证语句映射到断言和覆盖点。您可以调整覆盖目标,筛选特定的断言,并查看每个验证语句的详细信息。

你可以使用多个验证模型中的语句和断言块。

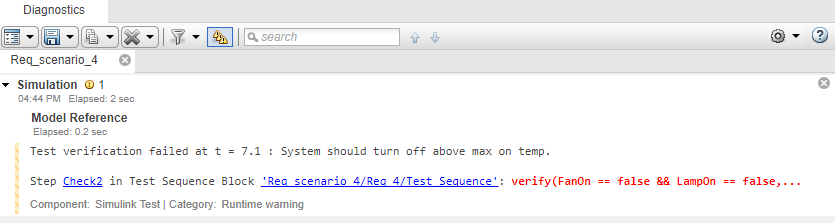

在Simulink中模拟设计时,如果断言或万博1manbetx验证评估失败。

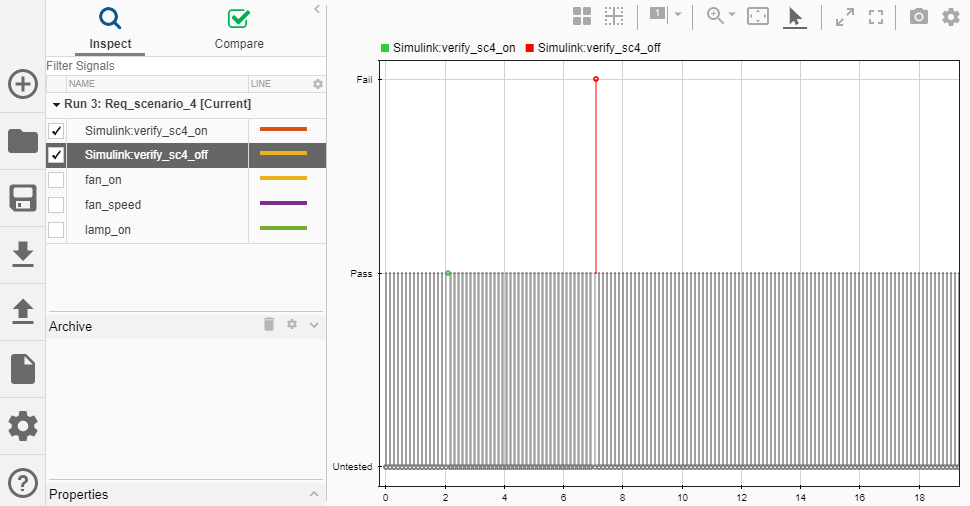

控件可以查看和检查模拟结果模拟数据检查器(万博1manbetx模型).打开模拟数据检查器在MATLAB中输入这段代码®命令提示符。

万博1manbetxSimulink.sdi.view

控件的左窗格中选择信号,即可查看随时间变化的信号模拟数据检查器.

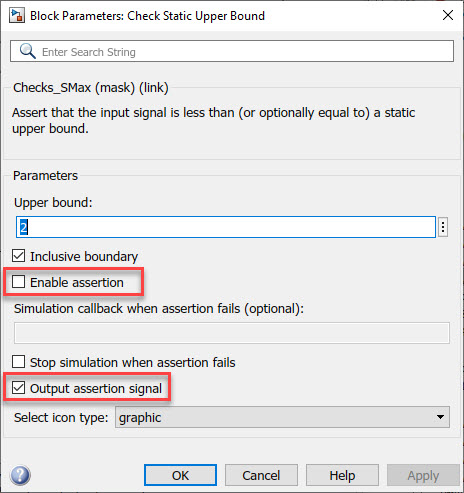

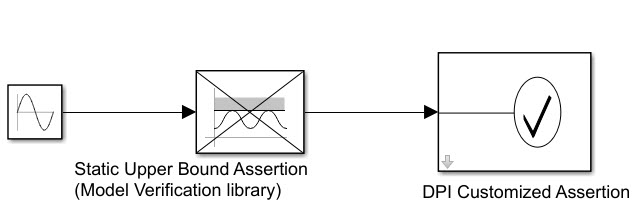

定制的断言

可以通过以下两种方式自定义SystemVerilog即时断言:

包括一个HDL验证器断言块,并自定义生成的SystemVerilog即时断言。您可以在断言失败时设置自定义消息,并且可以在断言失败时选择警告、错误或自定义命令。这是一个使用HDL验证器的例子断言块,看从Simulink生成本机SystemVerilog断言万博1manbetx.结果与该图相似。

要从Model Verification库定制断言,请将块输出连接到可定制的HDL Verifier断言通过以下步骤来阻止。

结果与该图相似。

生成UVM或SystemVerilog DPI组件

配置代码生成模型

在“配置参数”对话框中,选择代码生成在左边的窗格中。下目标选择,设置系统目标文件来systemverilog_dpi_grt.tlc或systemverilog_dpi_ert.tlc当使用嵌入式编码器®.

选择SystemVerilog DPI在左边的窗格中。下SystemVerilog港口,设置数据类型和连接设置。点击好吧.

生成UVM或SystemVerilog DPI组件

请注意

要生成UVM或DPI组件,断言或测试块必须在Simulink子系统中。万博1manbetx

在Si万博1manbetxmulink中,右键单击包含测试序列的子系统块,并选择C / c++代码>构建这个子系统.点击构建在打开的对话框中。

或者,您也可以使用MATLAB命令行生成DPI组件。使用slbuild(万博1manbetx模型)功能来构建系统。例如,要构建一个名为“My_verify_tst”的子系统,在MATLAB命令行中输入以下代码。

slbuild(“My_verify_tst”);

你也可以使用uvmbuild函数生成UVM测试台。如果您的测试模型包含验证语句,它们被映射到UVM环境中的断言,并收集覆盖率数据。

使用生成的组件运行HDL仿真

将当前文件夹更改为dpi_tb该文件夹位于HDL模拟器安装中的代码生成文件夹下。启动HDL模拟器,并运行生成的脚本以启动模拟。仿真输出与Simulink输出一致。万博1manbetx

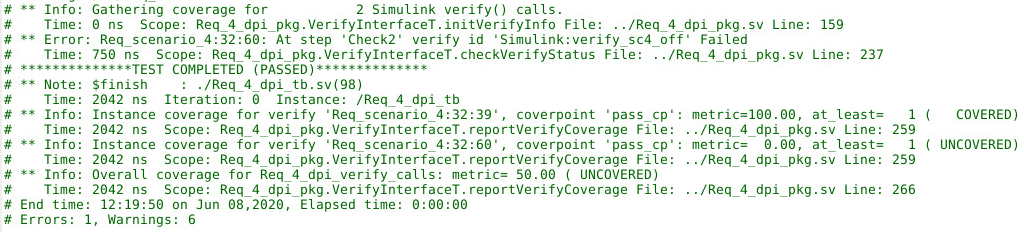

模拟完成后,将显示每个断言的覆盖率信息。默认情况下,如果断言至少计算了一次,则认为该断言已覆盖。

有关运行HDL模拟的其他信息,请参见根据Simulink数据验证生成的组件万博1manbetx.

筛选断言和覆盖报告

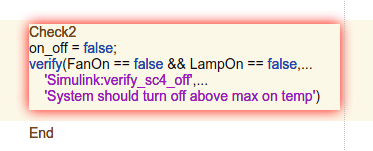

每个生成的错误或警告都显示一个标识其来源的唯一名称。该数字是该块的唯一Simulink标识符(SID)。万博1manbetx例如,该日志显示了一个由带SID的块生成的错误Req_scenario_4:32:60.

# **错误:Req_scenario_4:32:60: At step 'Check2' verify id 'Simul万博1manbetxink:verify_sc4_off' Failed

在一个测试序列中,您可能有几个步骤使用验证评估或多个DPI组件从模拟测井警告。在您的测试模型中,您可以过滤生成的输出验证将关联的SID指定为命令行上的加号参数,并将SID等同于-1.例如,关闭SID的所有输出和功能覆盖Req_scenario_4:32:60,在HDL命令行输入以下代码。

Vsim -c -sv_lib ../ Req_4工作。Req_4_dpi_tb + Req_scenario_4:32:60 = 1

调整功能覆盖目标

您可以使用断言块和验证语句在SystemVerilog模拟期间收集功能覆盖率。生成SystemVerilog后,使用uvmbuild或slbuild(万博1manbetx模型)函数,为每个断言定义覆盖目标。SystemVerilog模拟完成后,可以在生成的日志文件中查看结果,也可以使用第三方工具提取结果。默认的覆盖目标是至少执行一次断言或验证调用。

要增加特定断言的功能覆盖目标,请在命令行中指定关联的SID作为加号参数,并将SID等同于覆盖目标。例如,要增加一个的覆盖目标验证带SID语句Req_scenario_4:32:60从默认的1到2个通过检查,在HDL命令行输入以下代码。

Vsim -c -sv_lib ../ Req_4工作。Req_4_dpi_tb + Req_scenario_4:32:60 = 2

详细模式

默认情况下,当评估功能覆盖点并失败时,生成的DPI组件将输出一个错误。要查看功能覆盖点生成的其他输出,请输入参数+ VERBOSE_VERIFY在HDL仿真命令行。该参数添加了以下附加信息:

未测试的-未评估功能覆盖点时通过了-评估功能覆盖点,测试通过

例如,在使用ModelSim时®,在命令行输入此代码。

Vsim -c -sv_lib ../ Req_4工作。Req_4_dpi_tb + VERBOSE_VERIFY

Trace Generated SystemVerilog Error返回万博1manbetx源

在使用生成的测试序列运行SystemVerilog模拟之后,您的日志文件将显示警告和错误。要识别哪个块产生了特定的警告或错误输出,请使用hilite_system(万博1manbetx模型)函数。

例如,突出显示为SID生成警告的块Req_scenario_4:32:60,在MATLAB命令行输入此代码。

hilite_system(“Req_scenario_4:32:60”);

该图突出显示了验证语句和创建警告的测试序列块。

另请参阅

块

- 测试序列(万博1manbetx仿真软件测试)|测试评估(万博1manbetx仿真软件测试)|图表(Stateflow)|断言(万博1manbetx模型)|检查动态间隙(万博1manbetx模型)|检查动态范围(万博1manbetx模型)|检查静态间隙(万博1manbetx模型)|检查静态范围(万博1manbetx模型)|检查动态下界(万博1manbetx模型)|动态上界检查(万博1manbetx模型)|检查输入分辨率(万博1manbetx模型)|检查静态下界(万博1manbetx模型)|检查静态上界(万博1manbetx模型)|检查离散梯度(万博1manbetx模型)

MATLAB语言语法

- 验证(万博1manbetx仿真软件测试)

相关的话题

- 从Simulink测试验证调用生成SystemVerilog中的功能覆盖率万博1manbetx

- 生成SystemVerilog DPI组件

- UVM组件生成概述

- 验证语句(万博1manbetx仿真软件测试)