AXI4流接口生成模型设计

使用HDL Coder™软件,您可以在模型中实现一个简化的流协议。该软件在IP核中生成AXI4-Stream接口。

简化的流媒体协议

要将待测设计(DUT)端口映射到AXI4-Stream接口,请使用简化的AXI4-Stream协议。您不必对实际的AXI4-Stream协议建模,相反,您可以使用简化的协议。当你运行IP核心代在工作流中,生成的HDL代码包含包装器逻辑,该逻辑在简化的协议和实际的AXI4-Stream协议之间进行转换。简化的协议需要更少的协议信号,简化了有效信号和就绪信号之间的握手机制,并支持任意长度的突发。万博1manbetx

使用简化的AXI4流协议进行写和读事务。当您希望在IP核心中生成AXI4流接口时,在DUT接口中,实现以下信号:

数据

有效的

可选地,当您将标量DUT端口映射到一个AXI4-Stream接口时,您可以建模以下信号:

准备好了

其他协议信号,例如:

TSRTB

TKEEP

TLAST

TID

道明

摘要

数据和有效信号

当数据信号有效时,有效信号被断言。这个图说明了根据简化的流协议的数据和有效信号的关系。当您运行IP核生成工作流时,HDL Coder在HDL IP核中添加了一个流接口模块,该模块将简化的协议转换为完整的axi4流协议。在这个图中,时钟信号用clk表示。

基于样本的建模

当您想要在DUT边界上将数据信号模拟为样本流时,请以基于样本的模式建模。在基于样本的模式下,可以将数据信号建模为标量或向量。如果将数据信号建模为向量,请将采样打包维度设置为“全部”。在生成的HDL代码中,向量元素被打包在一起,整个向量被视为单个样本。您可以使用包装方式.看到样品的包装尺寸.

模型数据和有效信号万博1manbetx

包含使用启用的子系统来处理Data信号的算法。

使用Valid信号控制启用的子系统的启用端口。

例如,您可以直接将有效信号连接到启用端口。

您还可以在DUT中使用一个控制器,为已启用的子系统生成启用信号。

准备好信号(可选)

下游组件使用背压来告诉上游组件它们还没有准备好接收数据。DUT中的AXI4-Stream接口可以选择包括Ready信号。使用就绪信号:

在AXI4流从接口中应用背压。例如,当下游组件未准备好接收数据时,丢弃就绪信号。

响应AXI4流主界面中的背压。例如,当下游组件就绪信号低时,停止发送数据。

当您使用单个流通道时,默认情况下,HDL Coder生成Ready信号和处理背压的逻辑。背压逻辑将就绪信号连接到DUT使能信号。当输入主备信号低时,DUT被禁用,输出从备信号被驱动低。因为,HDL编码器产生背压逻辑和准备信号,当你使用一个单一的流通道,准备信号是可选的,你不需要在DUT端口建模这个信号。

当您使用多个流通道时,HDL编码器生成一个就绪信号,而不生成背压逻辑。在具有多个流通道的DUT中:

主通道忽略来自下游组件的Ready信号。

从通道就绪信号高,导致上游组件继续发送数据。

缺少背压逻辑可能导致数据丢失。要避免数据丢失,并在从属接口上施加背压,或在设计中响应主接口的背压,请执行以下操作:

为每个附加流接口建模Ready信号。

将建模就绪信号映射到附加接口的DUT端口。

当你不建模准备信号时设置目标接口task显示一个警告,其中提供了需要Ready端口的接口名称。如果您的设计不要求施加或响应背压,请忽略此警告。

如果在AXI4流接口中对就绪信号建模,则主接口会在就绪信号解除断言后的一个时钟周期内忽略数据和有效信号。一旦确认就绪信号,就可以开始发送数据和有效信号。在Ready信号解除断言后,您可以再发送一个数据和有效信号。

如果未对就绪信号建模,HDL编码器将生成该信号和相关的背压逻辑。此图根据简化流协议说明了数据、有效和就绪信号之间的关系。运行IP核心生成工作流时,HDL编码器会在HDL IP核心中添加一个流接口模块,用于将简化协议转换为完整的AXI4流协议。在此图中,时钟信号由clk表示。

例如,如果在DUT中有一个先进先出(FIFO)来存储一帧数据,以便向上游部件施加背压,则根据FIFO满信号对就绪信号建模。

请注意

如果启用延迟平衡,编码器将在就绪信号上插入一个或多个延迟。禁用就绪信号路径的延迟均衡。

其他协议信号(可选)

您可以选择建模其他AXI4-Stream协议信号。如果只建模所需的Data和Valid信号,编码器将生成TREADY和TLAST和AXI4-Stream协议信号。

如果您不建模的TLAST信号,编码器生成一个可编程寄存器的IP核,以便您可以指定您的数据包大小。详细的可编程数据包大小寄存器是在您的IP核生成报告。

框架建模

当您希望将数据信号模拟为DUT边界上的帧时,请使用基于帧的模式建模。在基于帧的模式下,将数据信号建模为矢量,并设置样本包装尺寸为None。看到样品的包装尺寸.

基于框架的模式对于软硬件系统交互的建模和仿真以及软件驱动程序代码的生成都很有帮助。

数据和有效信号建模要求

当您将向量端口映射到AXI4-Stream接口时:

连接每个DUT输入矢量数据端口到aSerializer1D块。

的Serializer1D块必须有一个ValidOut端口,并且Ratio设置为向量位宽。

连接每个DUT输出矢量数据端口到a反序列化器1d块。

的反序列化器1d块必须有一个ValidIn端口,并且Ratio设置为向量位宽。

将每个映射到AXI4-Lite接口的标量端口连接到率转换块。

中的比率率转换块中的比率必须匹配Serializer1D和反序列化器1d块。

每个映射到外部端口的标量端口必须与流算法子系统具有相同的采样时间。

流算法子系统遵循与标量端口映射到AXI4流接口的模式相同的数据和有效信号建模模式。看见Simulink中的模型数据和有效信号万博1manbetx.

例子

要将向量端口映射到AXI4-Stream接口,请打开hdlcoder_sfir_fixed_vector.slx模型在hdlcoder_sfir_fixed_vector.slx模型中,symmetric_fir块是流算法子系统。

具有多个流通道的模型设计

当你运行IP核心代工作流中,您可以将多个标量DUT端口映射到AXI4-Stream Master和AXI4-Stream Slave通道。当您使用向量端口时,您最多可以将端口映射到一个AXI4-Stream主通道和一个AXI4-Stream从通道。

请注意

如果您使用多个流通道,HDL编码器生成Ready信号,但不生成背压逻辑。如果你想让你的设计处理背压,在你的设计模型准备信号。

想要了解更多,请看生成具有多个AXI4流和AXI4主接口的HDL IP核.

有多个样品率的模型设计

当您运行IP Core Generation工作流时,对于具有多个采样率的设计,请使用HDL Coder软件。当您将接口端口映射到AXI4- stream主接口或AXI4- stream从接口时,要使用多个采样速率,请将映射到这些AXI4接口的DUT端口映射为以设计的最快速率或比设计速率慢的速率运行。

HDL编码器以比模型设计速率慢的速率运行映射到AXI4-Stream主接口和从接口的DUT端口:

每N个时钟周期,在第一个周期将AXI4-Stream主通道有效信号设置为高。例如,如果设计速率比慢速率DUT端口快8倍,每8个时钟周期的第一个时钟周期有效信号是高的。

在AXI4-Stream从接口上断言反向压力,以确保传入数据以每N个时钟周期一个数据帧的速率流。例如,如果设计速率比慢速率DUT端口快8倍,则第一帧在时钟周期1时流,第二帧在时钟周期9时流,以此类推。

当您将AXI4-Stream接口DUT端口映射到设计中的最快速率时,有效信号总是高的,以确保在AXI4-Stream从接口上没有背压。

在设计具有多个采样率的模型时,所有AXI4 Stream master接口映射的DUT端口必须以相同的速率运行。所有AXI4流从接口映射的DUT端口必须以相同的速率运行。

想要了解更多,请看多速率IP核生成.

AXI4流向量数据的接口选项

在具有矢量数据的模型上运行IP核心生成工作流时,可以使用样品的包装尺寸.将向量数据作为示例处理时,可以使用包装方式选择。

样品的包装尺寸

指定向量数据是作为样本处理还是作为帧处理。

一个也没有。这是默认值。当指定None时,向量被视为帧,向量元素一个接一个地流化。例如,当输入是第一个时钟周期中的6乘1向量时,第一个向量元素流化,第二个向量元素流化,以此类推。要使用此模式,模型必须包含用于输入的Serializer块和用于输出的反序列化块。的包装方式当样品的包装尺寸设置为None。

全部的当您指定All时,矢量将打包在一起并在单个时钟周期中传输。例如,当输入为六乘一矢量时,所有矢量元素将打包在一起,并在单个时钟周期中传输。在这种情况下,可以使用包装方式选择。

包装方式

属性时,指定如何打包向量元素样品的包装尺寸设置为“所有”。打包模式适用于AXI4-Stream从通道和主通道。在主通道上,数据使用位对齐或幂2对齐格式打包。在从通道上,数据将根据主通道的打包格式进行解包。

对齐。在这种模式下,向量元素直接挨在一起。如果打包的位宽小于AXI4-Stream通道宽度,那么打包的数据将用零填充以匹配通道宽度。

例如:

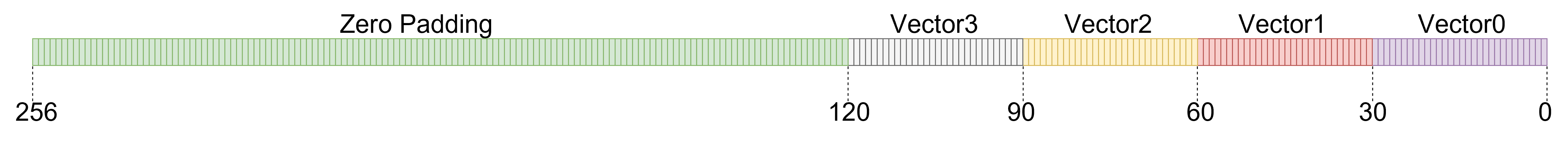

AXI4-Stream通道宽度为256位。

向量长度为30位,有4个向量帧。总数据宽度为120位。

当打包模式设置为位对齐时,AXI4流数据将按照此图中的方式打包

2的幂对齐。在这种模式下,向量元素首先被零填充到两个边界的最近幂。然后,填充的元素被打包在一起。如果压缩向量位宽度小于AXI4流通道宽度,则压缩数据用零填充以匹配通道宽度。

例如:

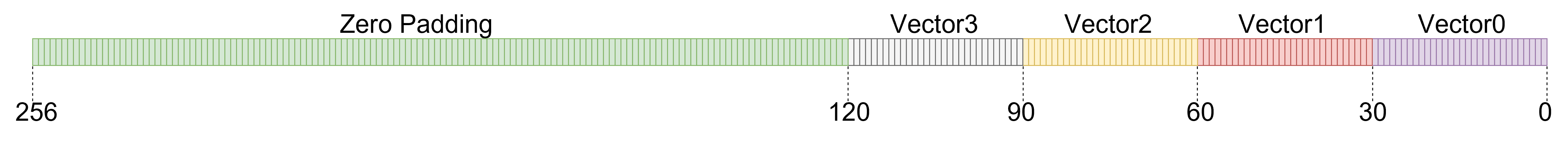

AXI4-Stream通道宽度为256位。

向量长度为30位,有4个向量帧。总数据宽度为120位。

当打包模式设置为2对齐的功率时,AXI4-Stream数据被打包,如图所示:

每个位宽为30的向量元素都被填充位宽为2的零,以将其扩展到32,即最接近2边界的幂次。

限制

将标量或矢量DUT端口映射到AXI4-Stream接口时:

赛灵思公司®Zynq®-7000或英特尔®第四的®Prime必须是你的目标平台。

锡林克斯万岁®或英特尔Quartus Prime必须是您的合成工具。

处理器/FPGA同步必须自由运行。

当您使用基于框架的建模时,您不能使用除Data和Valid之外的协议信号。例如,不支持Ready和TLAST。万博1manbetx