ミックスドシグナルシステム向けMATLABおよび仿真软万博1manbetx件

アナログシステムとミックスドシグナルシステムの解析,设计,検证

MATLAB®とS万博1manbetximulink的®を使用して,ビヘイビアモデリング,迅速な設計調査,設計前の解析,ミックスドシグナルシステムの検証を行います。

ミックスドシグナル集積回路(IC)の設計を始めるにあたり,混合信号Blockset™モデルの锁相环およびADCを使用できます。基本構成はデータシートの仕様で特徴づけられ,アナログ特性が含まれています。内蔵の解析ツールと測定テストベンチにより,検証作業の負担を軽減できます。

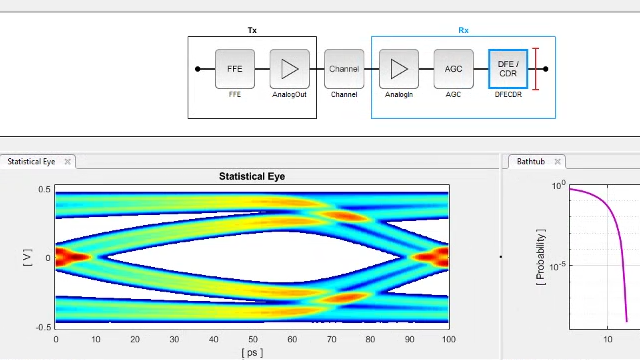

PCI Express的®,USB,DDR,イーサネットなどの高速リンクの设计と解析については,SerDes的工具箱™を使用して,チャネルイコライゼーションスキームを构筑して评価し,チャネルシミュレーション向けのIBIS-AMIモデルを自动的に生成できます。

MATLABとSi万博1manbetxmulink的を使用すれば,次のことが可能になります。

- PLL,DAC,ADC,串行解串器,开关电源,およびその他のミックスドシグナルシステムのビヘイビアモデルを作成

- トップダウン设计手法により,アナログ/デジタル设计のトレードオフを评価

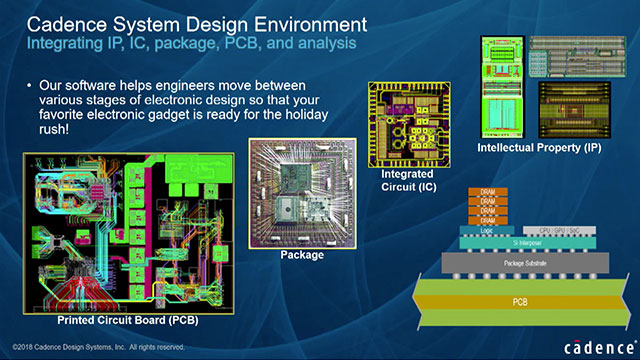

- コシミュレーションを通して,またはSystemVerilogモジュールとIBIS-AMIモデルの作成により,システムレベルのモデルをEDAツールに連携

- テストチップを制造する前に,アナログ/デジタルハードウェアおよび制御ロジックを含む设计を検证

「回路レベルのシミュレーションに3日かかりました.MATLABとSimu万博1manbetxlink中の使用により,シミュレーション时间をわずか1分に短缩できました。」

君上原,Epson Toyocom公司

MATLABによるミックスドシグナルシステムの设计

ミックスドシグナルの解析

最高レベルで抽象化すると,MATLABを使用して基本的なシステムアーキテクチャを解析できます。たとえば,2次シグマデルタ変调器と3次シグマデルタ変调器の优劣や,最适なPLLのタイプ,ボード线図から読み取れるシステムの安定性,などを解析できます。

MATLABとSi万博1manbetxmulink中の解析ツールを使用して设计空间を探索し,最适な设计の起点を见つけます。たとえば,混合信号模块库では,MATLABの机能を使用して,PLLの闭ループおよび开ループの静的解析を実行し,ループフィルターを迅速に设计します。

MATLABは,スプレッドシートやC / C ++言语などの従来のプログラミング言语に优る解析机能と可视化机能を提供します。ただし,既存の投资を放弃する必要はありません。MATLABは,微软®高强®およびC / C ++言语に対応しています。

ミックスドシグナルのトップダウン设计

ビヘイビアモデルと測定テストベンチを使用して詳述し,さらに迅速な設計と検証を可能にします.万博1manbetxSimulinkでは,さまざまな抽象化レベルで,制御ロジックやデジタルハードウェアと共にアナログ回路をシミュレーションできます。

“伝達関数”の抽象化レベルで連続時間信号,またはSimscape电气™のいずれかを使用してアナログ回路を記述し,電圧と電流,およびRLC要素,オペアンプ,スイッチなどのコンポーネントをモデル化します。

浮动小数点精度を使用して,アルゴリズムレベルでデジタル回路について记述するか,または量子化效果および饱和效果を含む任意长の固定小数点データ型を使用して,ビット精度シミュレーションを実行します。最后に,ASICとFPGAをターゲットとする合成可能なHDLコードを生成します。

MATLAB关数またはStateflow的®を使用して,制御ロジックとステートマシンをアルゴリズムレベルで記述します。固定小数点データ型を使用し,組み込みC / c++コード生成を使用してマイクロコントローラーをターゲットとするか,ASICおよびFPGAをターゲットとする合成可能なHDLコードを生成するかを決定できます。

ミックスドシグナルの検证

システムレベルモデルは,设计フローの次の段阶に关连付けられている必要があります.MATLABモデルとSi万博1manbetxmulink的モデルをSPICEモデル,HDLコード,ハードウェア向けのテストハーネスとして使用するには,さまざまな方法があります。

コシミュレーションは異なるツール間のランタイムリンクです。シミュレーションのタイムステップごとに,ツール間でデータが交換されるため,それらを一緒に実行してモデルをシミュレーションできます。アナログドメインでは,抑扬顿挫®艺术大师®AMS设计师が的Simulin万博1manbetxkへのコシミュレーションリンクを提供します。デジタルドメインでは,HDL验证™が,ループテスト用のサードパーティ制HDLシミュレータおよびFPGAボードへのリンクを提供します。

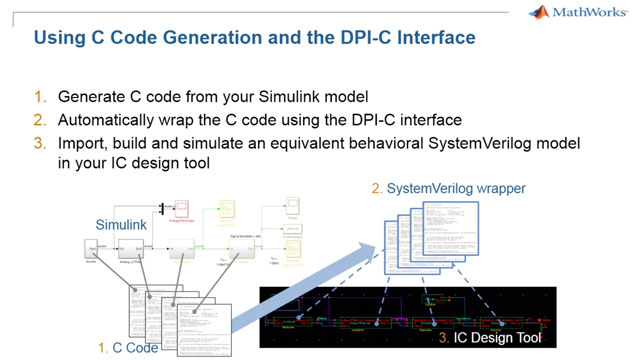

回帰テストや机能検证环境での再利用のために,DPI-Cインターフェイスを活用して,MATLABアルゴリズムとSim万博1manbetxulink的モデルを的SystemVerilogモジュールとしてエクスポートできます。

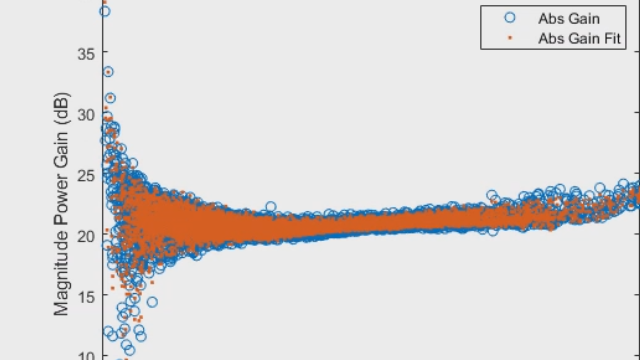

MATLABを使用してICシミュレーション結果を解析し,データをより効果的に可視化し,最適化,機械学習,深層学習の手法を使用してビヘイビアモデルをさらに調整できます。

ミックスドシグナル検证の最终段阶は,デバイステストです。この段阶では,MATLABとSi万博1manbetxmulink中は様々なテスト机器と统合され,モデルを介してテストベクトルを作成するテストシステムを构筑し,テスト机器を制御して,结果を解析できます。

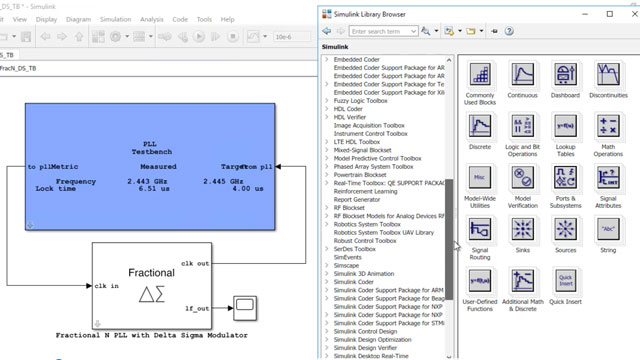

位相同期回路(锁相环)

トランジスタレベルのモデルは正确ですが,位相同期回路(PLL)の设计においては,速度が非常に遅くなります。多くの场合,フィードバックループでは,ロック时间の取得には长时间のシミュレーションを要し,位相ノイズの影响の正确な予测にはシミュレーションの小さなタイムステップを要します.万博1manbetxSimulinkと混合信号模块库は,オーバーサンプリングを必要とせず,可変ステップソルバーを使用して非常に高速なPLLシミュレーションを実现します。

従来の制御设计を継承するS万博1manbetximulink中には,フィードバックループで非常に效率的にシステムをシミュレーションできるシミュレーションエンジンが搭载されています。ビヘイビアモデリングとより迅速なシミュレーション方法を组み合わせることで,PLL设计のシミュレーション时间を数日から数时间または数分に短缩できます。

データコンバーター(ADC和DAC)

アナログ——デジタルコンバーター(ADC)の設計と検証においては,連続時間信号と離散時間信号を迅速にシミュレーションできる能力が重要となります.Sim万博1manbetxulinkでは,同じ環境のアナログハードウェアとデジタルハードウェアでモデリングを実行できるため,香料ツールで必要となる時間のわずかな時間でADCを設計できます。

万博1manbetxSimulink的を使用すると素早くADCを设计できるため,エンジニアはより迅速にパラメータースイープを行い,より短い时间で详细な検证を実行できます.Mixed信号模块库のテストベンチを使用すると,积分非直线性误差(INL),微分非直线性(DNL),ノイズ性能を迅速に评価できます。

并行转换器および高速リンク

高いデータレートで動作する并行转换器シリアルイコライゼーションシステムとDDRパラレルイコライゼーションシステムの解析およびシミュレーションを行うことで,シミュレーションの速度が大幅に低下する可能性があります。速度が低下した場合,プロジェクトに納期遅れのリスクが生じ,設計調査の範囲が制限されます。

SerDes的设计师アプリを使用すると,NRZ信号またはPAM4信号を使用して,プリエンファシスおよびイコライゼーション向けのさまざまなアーキテクチャを含む,任意の高速チャネルイコライゼーションスキームをわずか数分で解析できます。アプリからは,Simulink的モデ万博1manbetxルを自动的に生成して适応等化アルゴリズムをさらに调整できます。または,独自のモデルから始めて,独自に开発したアルゴリズムを追加することもできます。システム统合とチャネル検证を行うために,SerDes的工具箱を使用してIBIS-AMIモデルを自动的に生成できます。

射频パワーアンプのデジタルプリディストーション(DPD)

デジタルプリディストーションは理论的には単纯ですが,実践には困难を伴います.MATLABは,RFパワーアンプ(PA)がもたらす影响を详しく理解しながら,テスト机器の制御,复雑なデータの解析,DSPまたはFPGA用のアルゴリズムの构筑を行うための,统一された环境を提供します。

MATLABでは,変更済みの沃尔泰拉シリーズに基づいて,メモリや非线形性を含むPAモデルを简単に构筑し,RF模块集™电路包络を使用してシミュレーションできます。独自のDPDアルゴリズムを使用して,闭ループでRF PAをシミュレーションすることで,ラボテストに移る前に,量子化,その他のRF效果を予测できます。