主要内容

锁相环

模拟锁相环(PLL)系统的设计与仿真

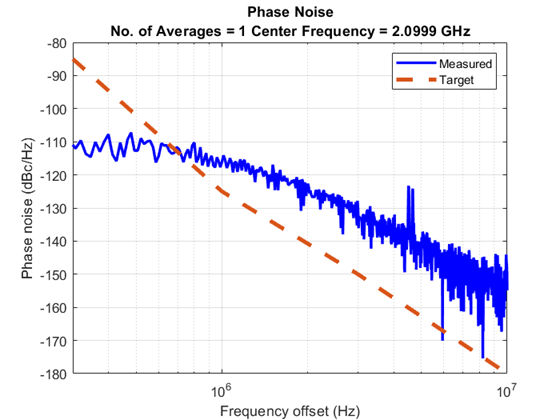

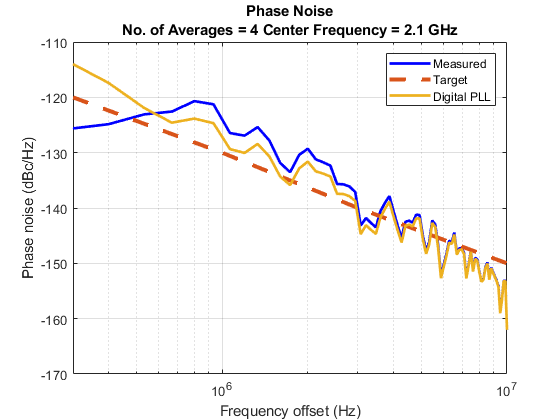

设计一个PLL系统,从基本的基础块或一个参考架构系列开始。模拟和分析PLL系统,以验证关键性能指标,直到满足系统规范。

您可以通过提供每个基础块的规格和损伤,并将块连接到模拟不同的PLL架构模型(自下而上的方法)。或者,您可以从典型的PLL架构的完整系统级模型开始,并在满足您的系统规格(自上而下的方法)之前自定义这些模型。

使用测量和测试窗格在整个设计过程中,验证砌块和整个系统的规范是否存在缺陷。

阻碍

话题

此示例演示如何使用参考体系结构设计简单锁相环(PLL),并使用PLL测试台对其进行验证。