用于半导体开发的MAT万博1manbetxLAB和Simulink

MATLAB®和仿真软万博1manbetx件®便于设计空间探索和自上而下的半导体器件的设计,让工程师合作,描述,分析,模拟和建模使用的组合方法和抽象级别验证他们的多域系统。域的例子是模拟,数字,RF,软件,和热;和抽象可以从晶体管级到算法水平而变化。

建模阶段后,系统模型,验证环境,并在MATLAB和Simulink定义测试用例可以在EDA工具可以重复使用,连接系统的设计与实现。万博1manbetx这些功能使工程师能够显著缩短了设计迭代,减少项目进度延迟的风险,并启用的规格和设计变更的持续集成。

“使用MathWorks工具,我们确定最好的算法的选择。由于模型跑得比我们的电路仿真器快得多,我们抓住了执行错误,更快,缩短了产品上市时间。”

Cory Voisine,快板微系统

使用MATLAB和Simulink万博1manbetx的半导体发展

数字化设计

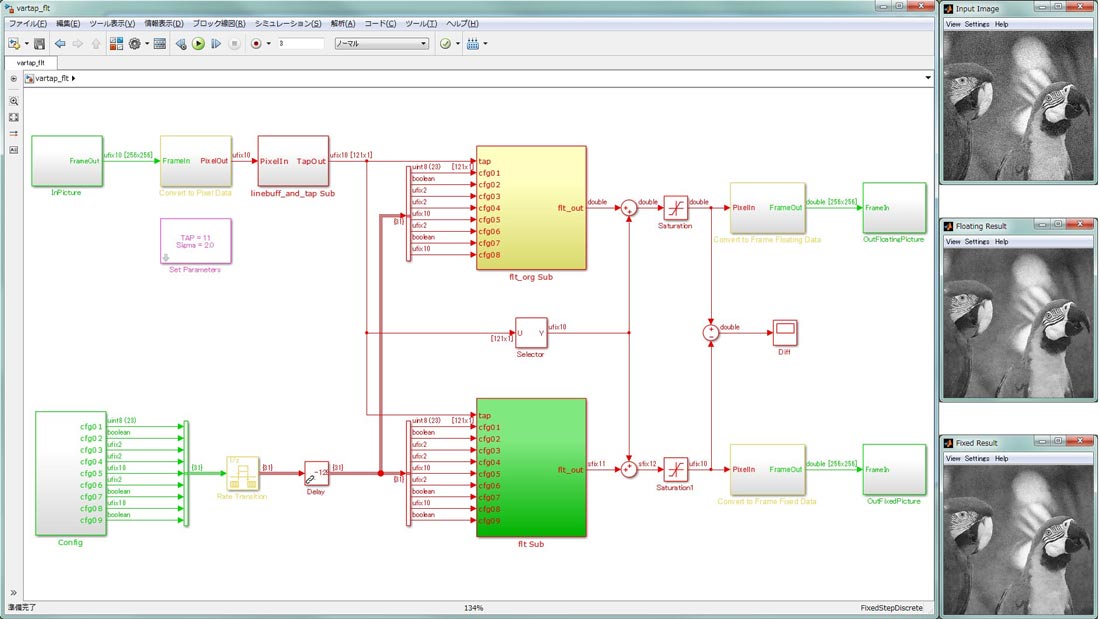

模型,并使用状态图,数学函数,信号处理算法,和数字逻辑扩展库模拟数字系统。用抽象的水平,使精度和仿真速度之间的权衡权构建您的模型。这允许快速和有效的设计空间探索,帮助您做出的系统架构正确的选择,数据类型。此外,现有的Verilog®,VHDL®,可以导入C/ c++模型,支持自顶向下/自底向上的混合设计流。

演出系统级芯片(SoC)的硬件/软件协同设计和模拟利用MATLAB和Simulin万博1manbetxk,考虑了SoC的体系结构以及任务执行和操作系统的影响。这允许在产品开发过程的早期对软件性能和硬件利用率进行高保真分析。

验证

验证以结构化方式MATLAB和Sim万博1manbetxulink模型,定义验证环境,测试案例,和正规性。回归测试工具和正式的引擎有提供,让您在设计流程的早期发现缺陷。为了量化的验证结果,覆盖度量和可追溯性要求工具提供。

导出系统模型,验证环境和测试用例SystemVerilog的DPI-C组件和再利用他们作为司机,跳棋,或在您的EDA仿真参考模型。您还可以使用cosimulation与他们的HDL或SPICE表示比较MATLA万博1manbetxB和Simulink模型。

RTL实现

专注于设计选项,而不是编码:逐步细化验证的数字系统的模型和将它们转换为RTL代码。实现选择可以在MATLAB和Simulink来表达,这样生成的RTL代码准确地反映了设计者的意图。万博1manbetx相对于手动编码,这个工作流程不仅允许不同的架构选择更快的探索,但它也使整个过程更加敏捷,快速适应变化。

实现数字MATLAB和Simulink模型到使用FPGA功万博1manbetx能于中环流最常见的FPGA开发板。这可能是两个ASIC和FPGA设计的原型设计和验证非常有帮助。