FPGA-in-the-Loop

在模拟器和电路板之间创建一个fpga在环链接,使您能够:

与Simulink中的算法直接验证HDL实现万博1manbetx®或MATLAB®。

将Simulink或MATLAB中的数据和测试场景应用到FPGA上的H万博1manbetxDL设计中。

将现有的HDL代码与在Simulink或MATLAB中开发的模型集成。万博1manbetx

在使用fpga -in- loop (FIL)模拟之前,您必须下载您的板的支持包。万博1manbetx看到下载FPGA单板支持包万博1manbetx。或者,您可以手动创建自定义板定义文件用于FIL模拟。看到FPGA板定制。

下载单板支持包后,选择一个仿真工作流。万博1manbetx看到FPGA-in-the-Loop模拟工作流。要了解FIL模拟是如何工作的,请参见FPGA-in-the-Loop模拟。

应用程序

| FPGA-in-the-Loop向导 | 生成一个fpga -in- loop (FIL)块或系统对象从现有的HDL文件 |

对象

hdlverifier。FILSimulation |

费尔仿真与MATLAB |

功能

programFPGA |

在FPGA上加载编程文件 |

块

| 费尔模拟 | 在FPGA硬件上模拟HDL代码万博1manbetx |

主题

概述

选择生成块还是系统对象™,并决定是使用FIL Wizard还是HDL Workflow Advisor。

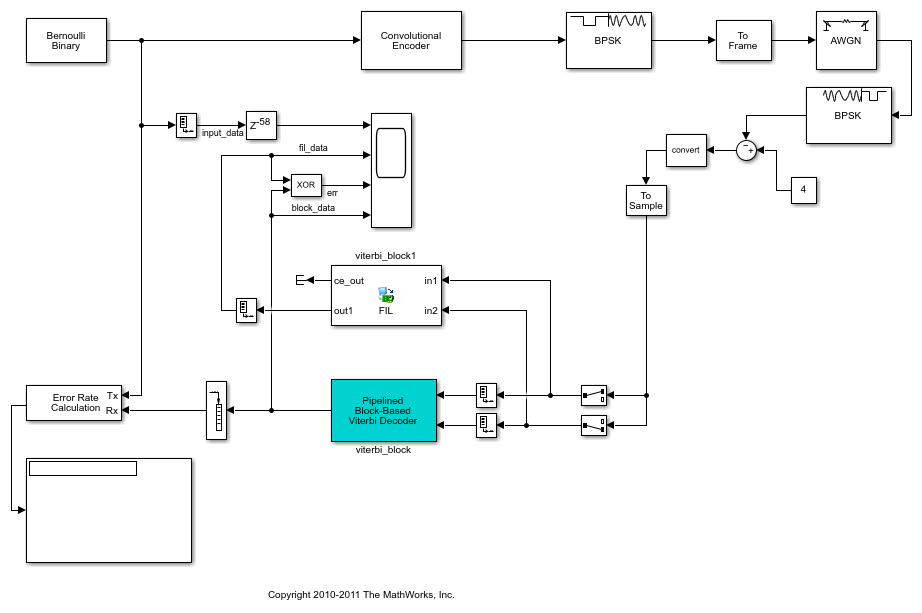

fpga在环(FIL)仿真提供了使用Simulink或MATLAB软件在真实硬件中测试任何现有HDL代码设计的能力。万博1manbetx

FIL要求及准备

模块和系统对象的FIL模拟DUT指南。

FPGA板支持包包含所有支持的万博1manbetx板的定义文件,用于FPGA-in- loop (FIL)仿真,数据捕获,或MATLAB AXI主。

将MATLAB路径设置为Xilinx®, Microsemi®,英特尔®软件

介绍自动支持包设置过程中的步骤,用于配置与fpga在环中使用的硬件。万博1manbetx

描述为FIL准备硬件和硬件工具所需的步骤。

从遗留代码生成FIL接口

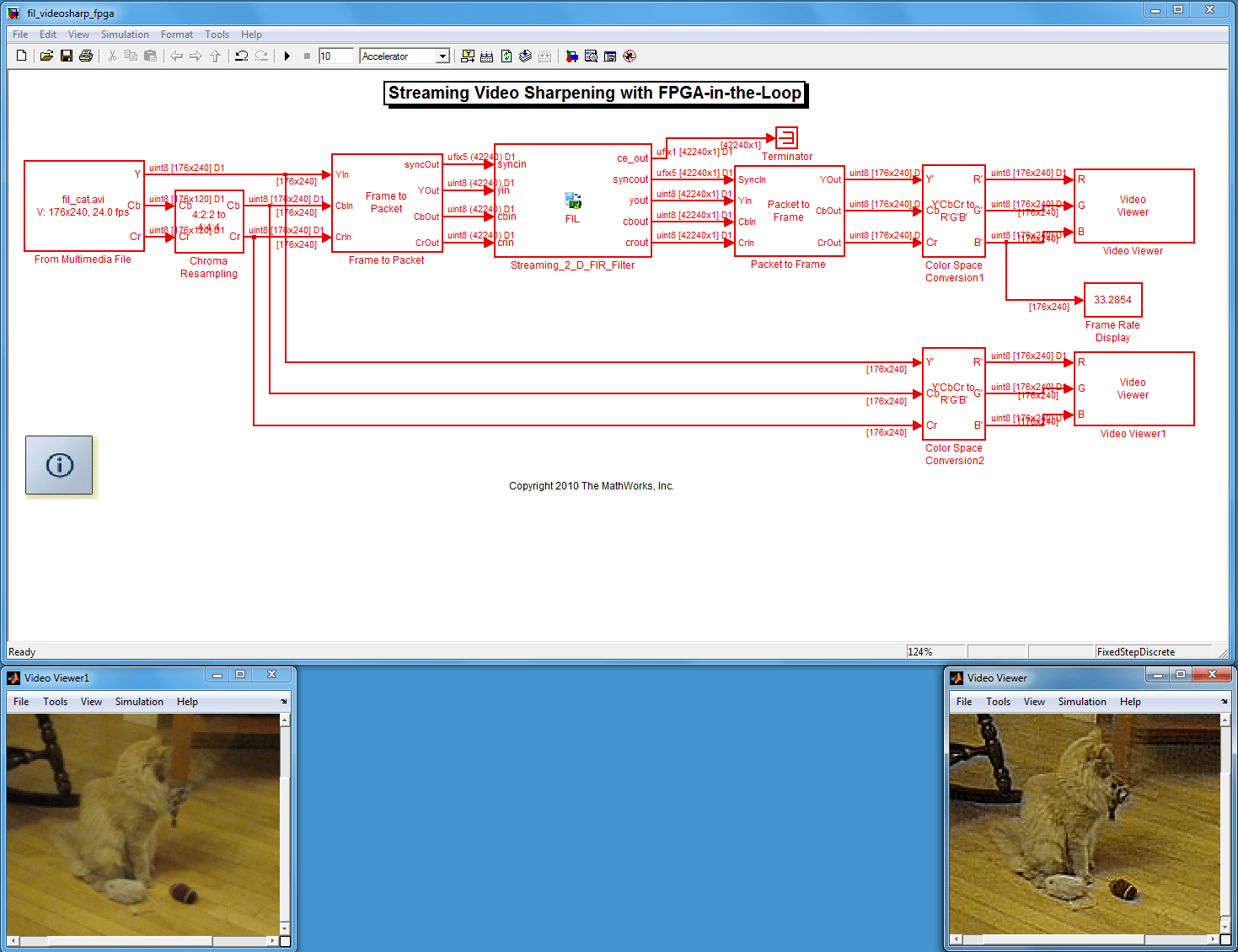

从现有的HDL源文件生成一个FPGA在环块,然后在Simulink仿真中包含FPGA实现。万博1manbetx

从现有的HDL源文件生成一个FPGA在环系统对象,然后在MATLAB仿真中包含FPGA实现。

这个示例向您展示了如何使用HDL验证器™设置fpga在环(FIL)应用程序。

这个例子向您展示了如何使用fpga在环仿真验证Filter design HDL Coder™生成的数字上变频器设计。

从MATLAB代码生成FIL系统对象(需要高密度脂蛋白编码器许可)

使用HDL Workflow Advisor生成一个fpga在环系统对象和测试台。

从Simulink模型生成FIL块(需要万博1manbetx高密度脂蛋白编码器许可)

使用HDL工作流顾问生成测试台并启用代码覆盖率(高密度脂蛋白编码器)

使用HDL Workflow Advisor为生成的HDL代码生成测试平台和代码覆盖率。

在Simulink中使用HDL Workflow Advisor进行FIL仿真万博1manbetx

使用HDL Workflow Advisor生成一个fpga在环模型。

故障排除

修复了常见的错误消息和问题。